# Apple //e Hardware

Jim Sather

# **Apple //e Hardware**

**Jim Sather**

**Ampersand Verlag, Berlin**

Titel der englischsprachigen Originalausgabe:

*Understanding the Apple IIe*

© Copyright 1985 Quality Software

Deutsche Übersetzung: Arne Schäpers

© Copyright 1986 Ampersand Verlag GmbH, Berlin

ISBN: 3-89058-040-8

Printed in West Germany

# Inhalt

|                                                                                                                                                                                                                                                                               |           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| <b>Kapitel 1 - Der Apple //e - ein Überblick</b>                                                                                                                                                                                                                              | <b>1</b>  |

| Ein Abriß des Apple //e                                                                                                                                                                                                                                                       | 1         |

| <i>Der Mikroprozessor und die Busstruktur 1, Speicherbausteine, Datenorganisation und Adreßdekodierung 3, Die Steckplätze für Zusatzkarten 5, Der spezielle Steckplatz 5, MMU, IOU und HAL 6, Die Videoausgabe 8, Die Tastatur 11, Weitere I/O 12, Die Stromversorgung 14</i> |           |

| Zusammenfassung                                                                                                                                                                                                                                                               | 14        |

| <b>Kapitel 2 - Die Busstruktur des Apple //e</b>                                                                                                                                                                                                                              | <b>17</b> |

| Computerbusse und tri-State-Logik                                                                                                                                                                                                                                             | 17        |

| Die Schubfach-Analogie                                                                                                                                                                                                                                                        | 22        |

| Die CPU, der RAM und der ROM                                                                                                                                                                                                                                                  | 22        |

| Die Adressierung des RAM und die Verteilung der Datenbits                                                                                                                                                                                                                     | 23        |

| <i>Der gemultiplexte RAM-Adreßbus 24, Der Videoscanner 24, Die Verteilung der RAM-Daten 26</i>                                                                                                                                                                                |           |

| Die Adreßdekodierung                                                                                                                                                                                                                                                          | 27        |

| Eingabe und Ausgabe                                                                                                                                                                                                                                                           | 32        |

| <i>Die Eingabe von der Tastatur 32, Die Steckplätze 34, Ein-/Ausgabe zusammen mit Diskettenlaufwerken 34, Direkter Speicherzugriff (DMA) 35, Der serielle Eingangsmultiplexer 35, Die seriellen Ausgänge 36</i>                                                               |           |

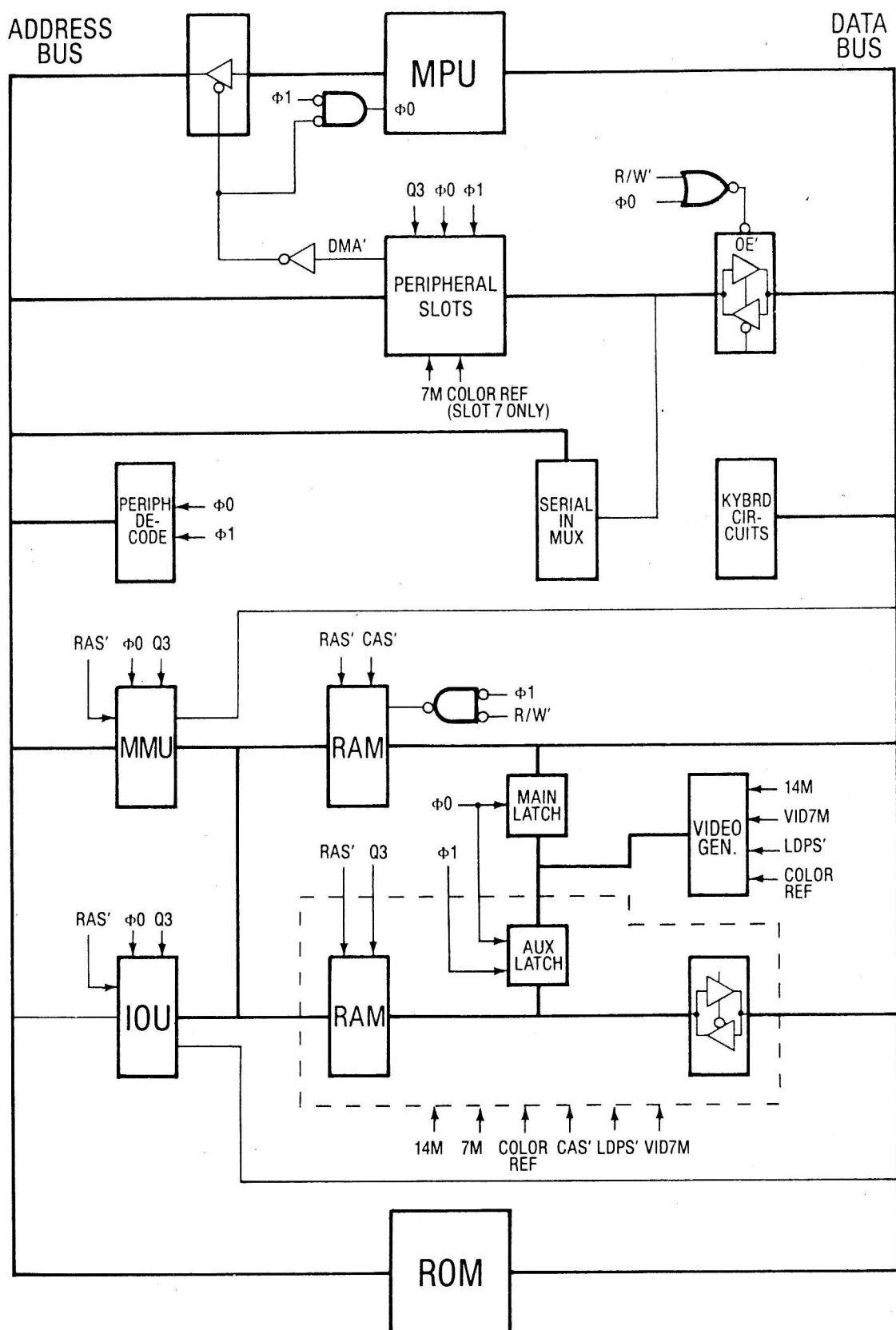

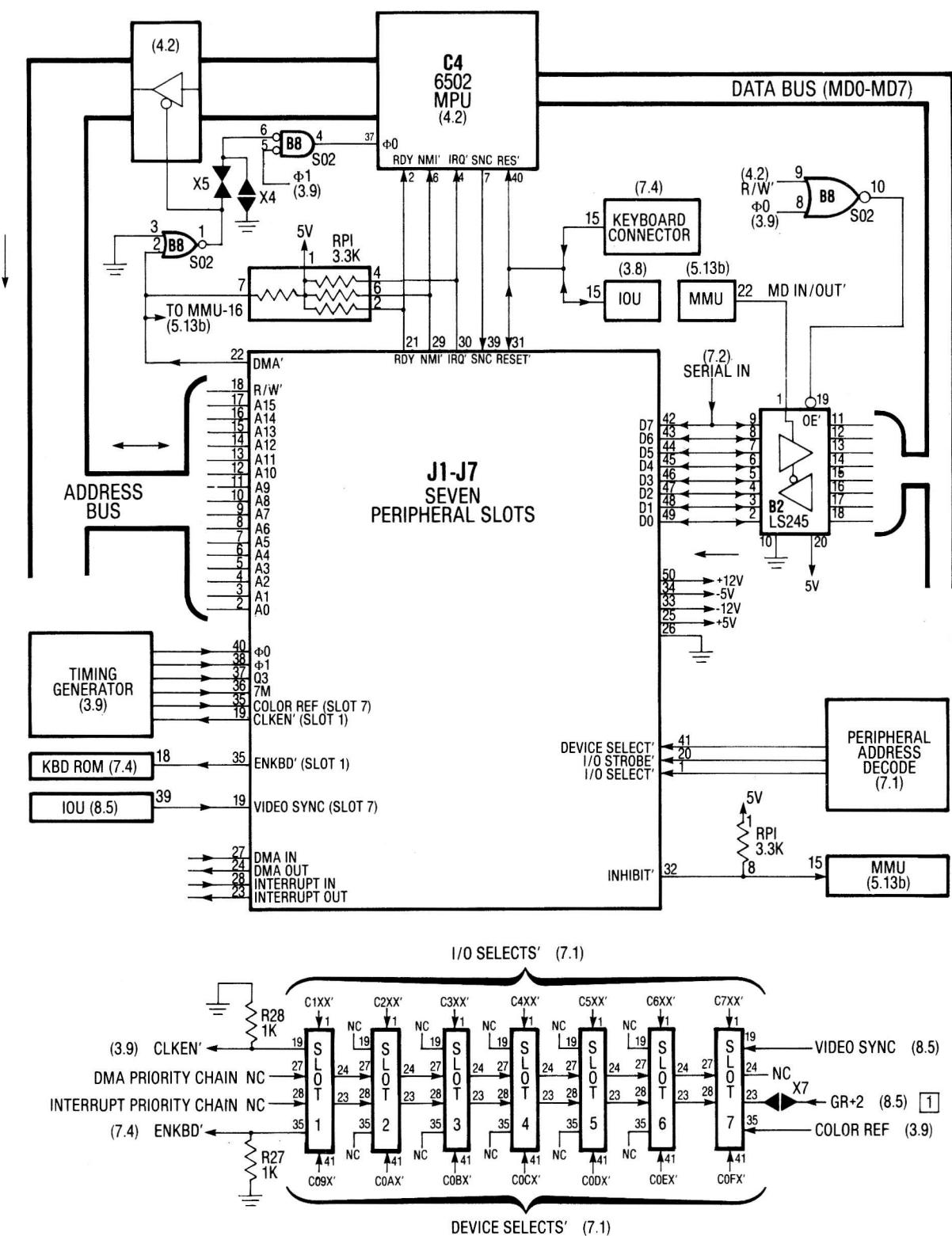

| Die vollständige Busstruktur                                                                                                                                                                                                                                                  | 38        |

| <b>Kapitel 3 - Die Takterzeugung und der Videoscanner</b>                                                                                                                                                                                                                     | <b>39</b> |

| Abriß des Taktgenerators                                                                                                                                                                                                                                                      | 39        |

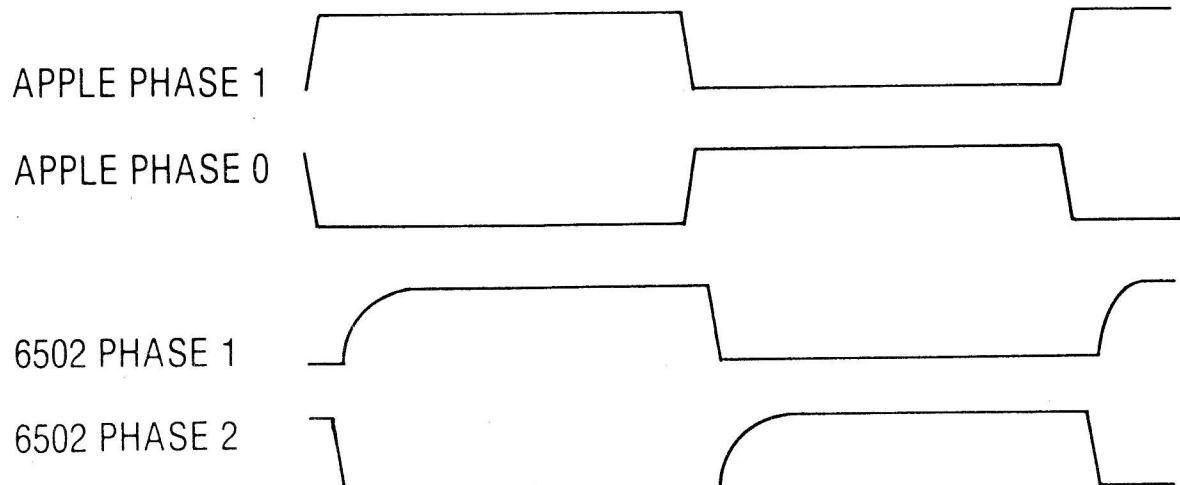

| Die Taktsignale                                                                                                                                                                                                                                                               | 40        |

| Die genauen Frequenzen                                                                                                                                                                                                                                                        | 42        |

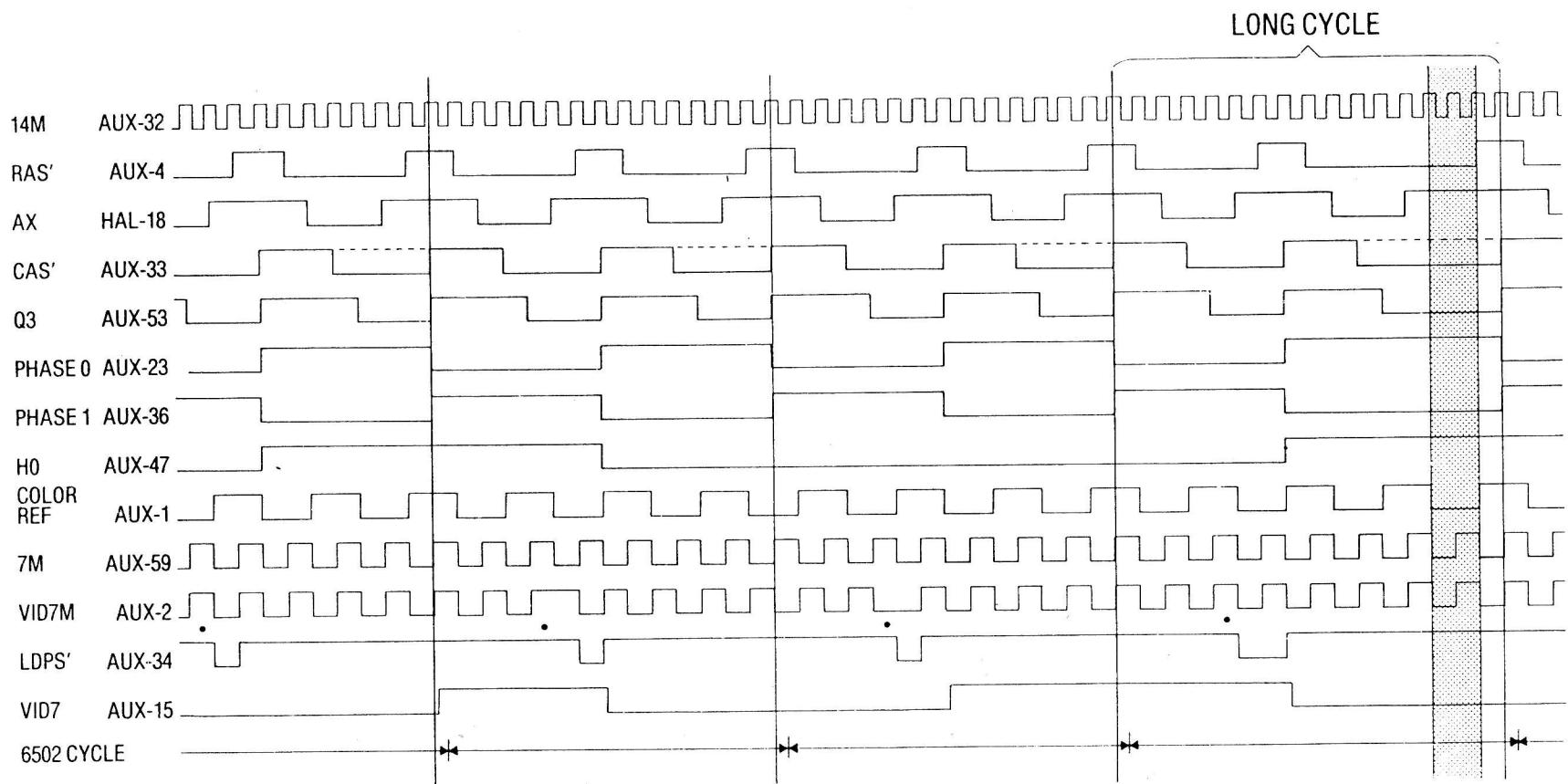

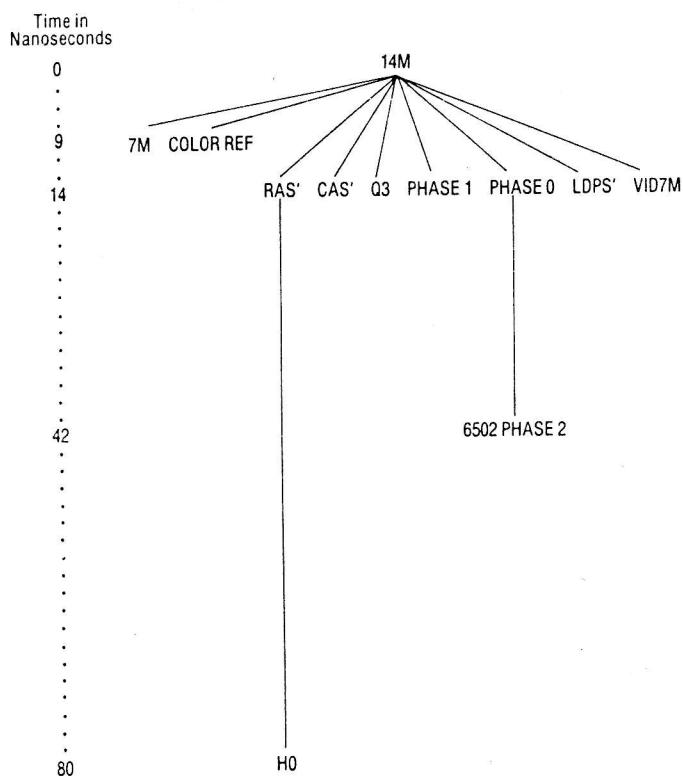

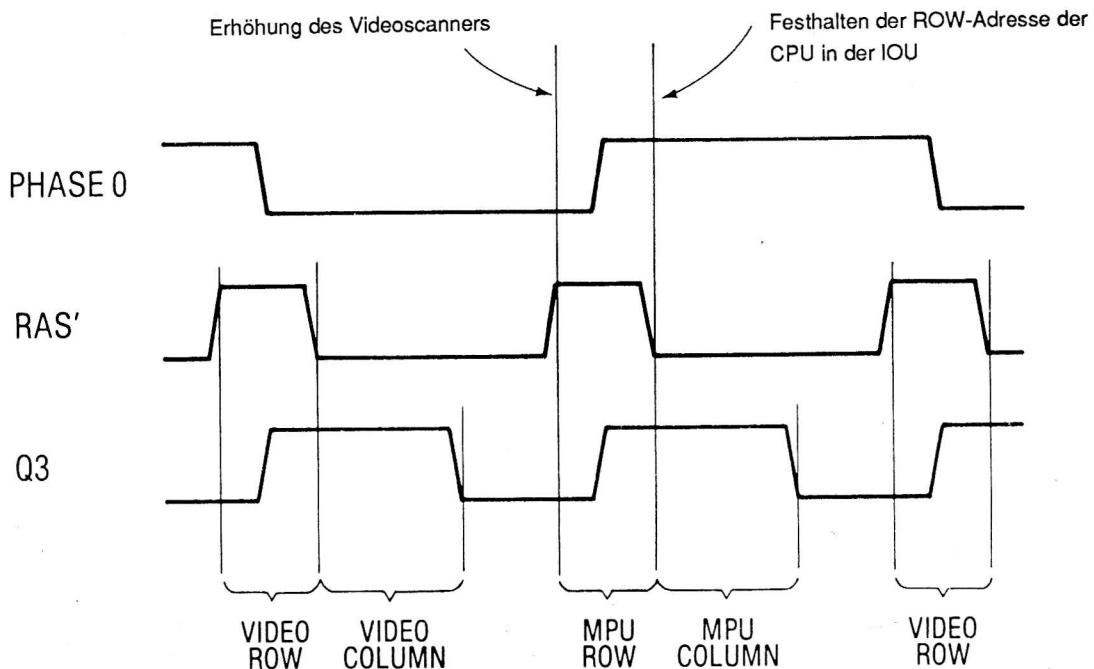

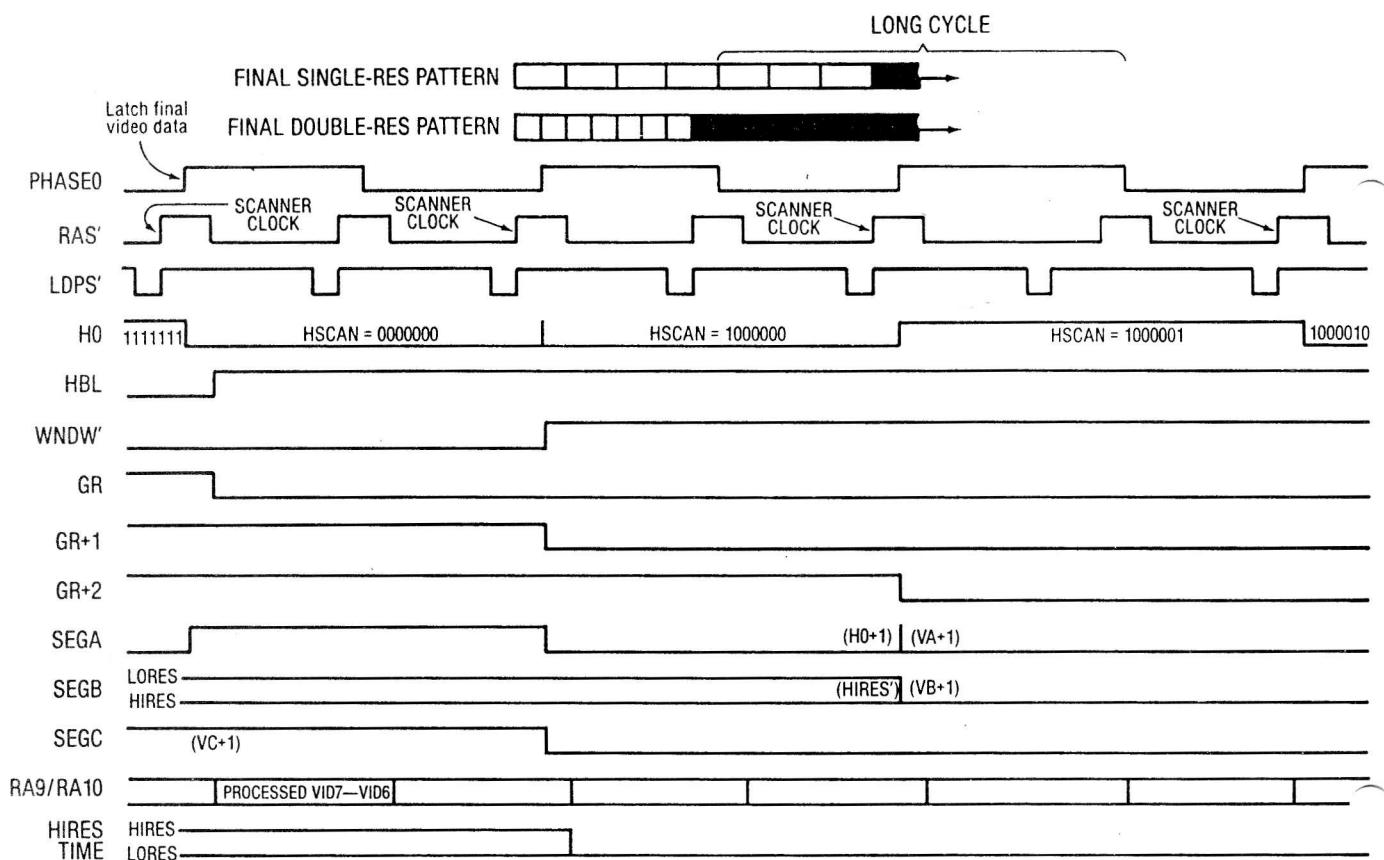

| Das Zeitdiagramm                                                                                                                                                                                                                                                              | 43        |

| Die Verteilung der Taktsignale                                                                                                                                                                                                                                                | 46        |

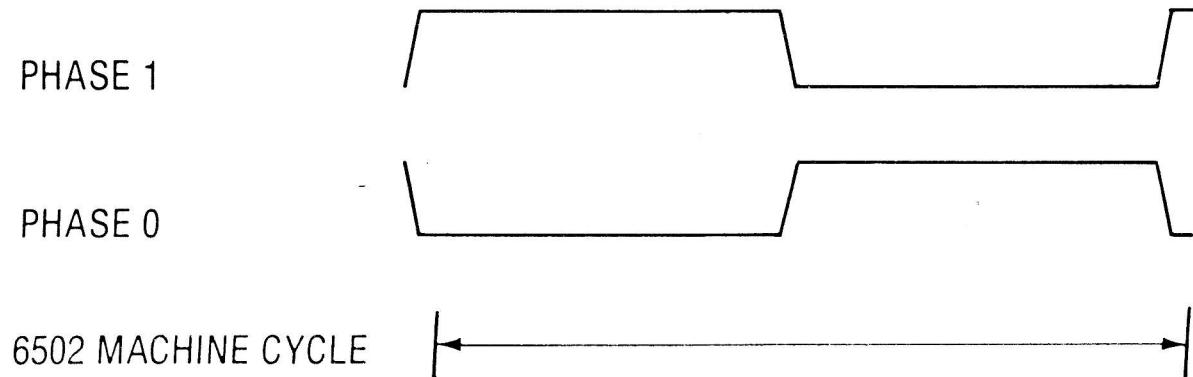

| Detaillierte Beschreibung der Taktsignale                                                                                                                                                                                                                                     | 46        |

| <i>PHASE0 und PHASE1 46, 14M, 7M und COLOR REFERENCE 48, RAS', CAS' und Q3 49, LDPS' und VID7M 50</i>                                                                                                                                                                         |           |

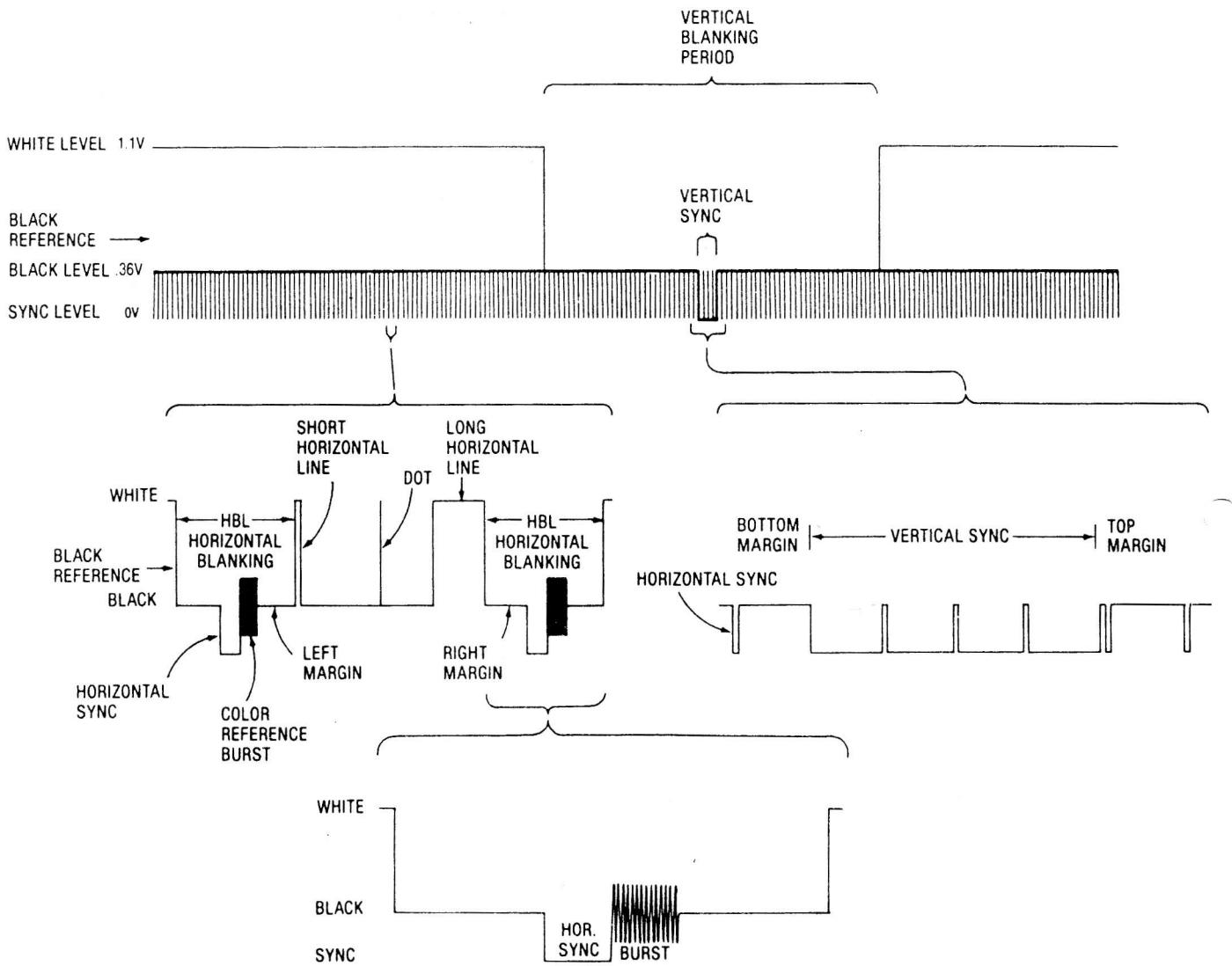

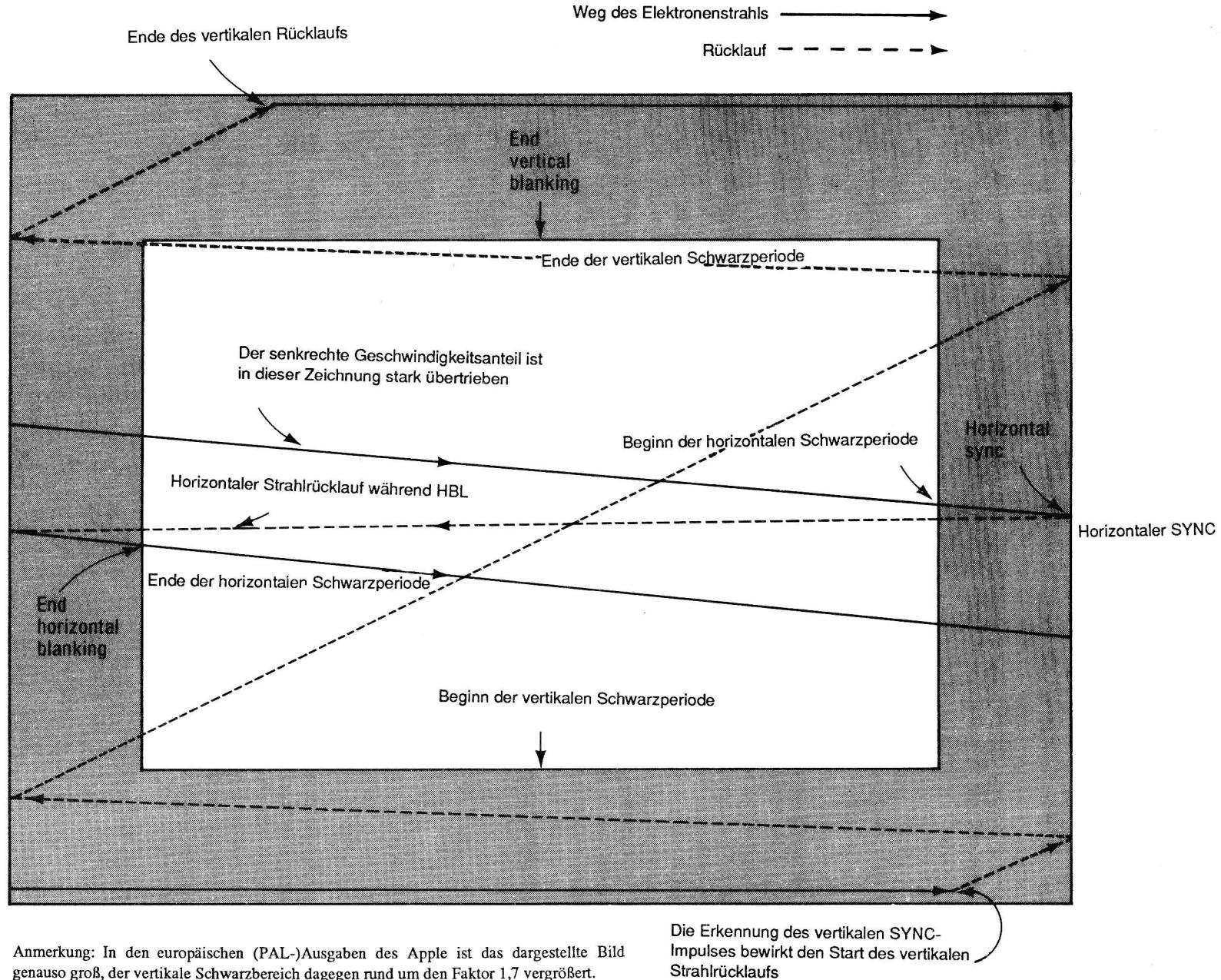

| Der Aufbau eines Fernsehbildes                                                                                                                                                                                                                                                | 51        |

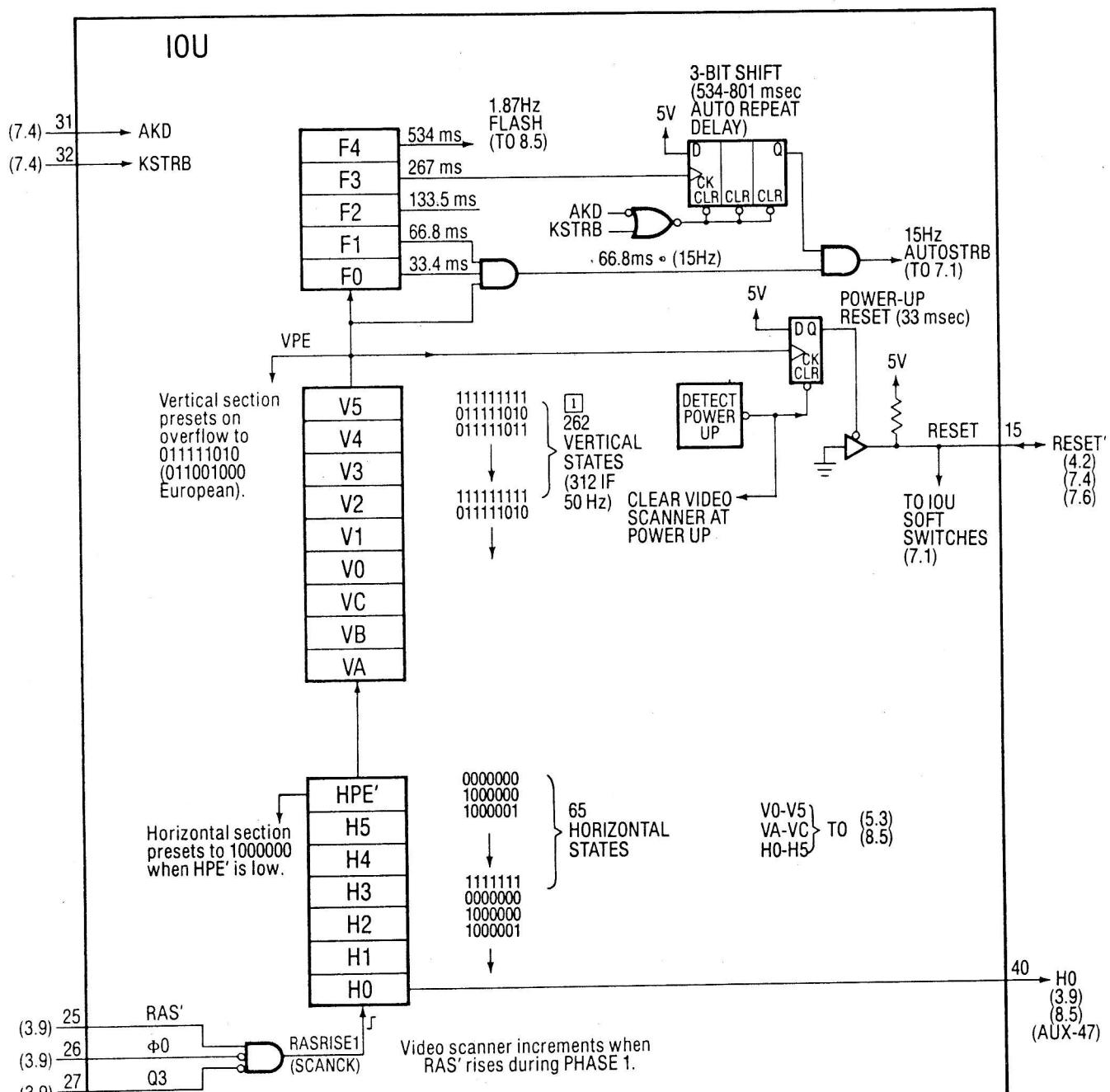

| Der Videoscanner                                                                                                                                                                                                                                                              | 52        |

| <i>Der Horizontalzähler 52, Der Vertikalzähler 54, Andere Modelle und der Videoscanner 54, Der Flash-Zähler und "Power-up" RESET 57</i>                                                                                                                                       |           |

| Der lange Zyklus                                                                                                                                                                                                                                                              | 58        |

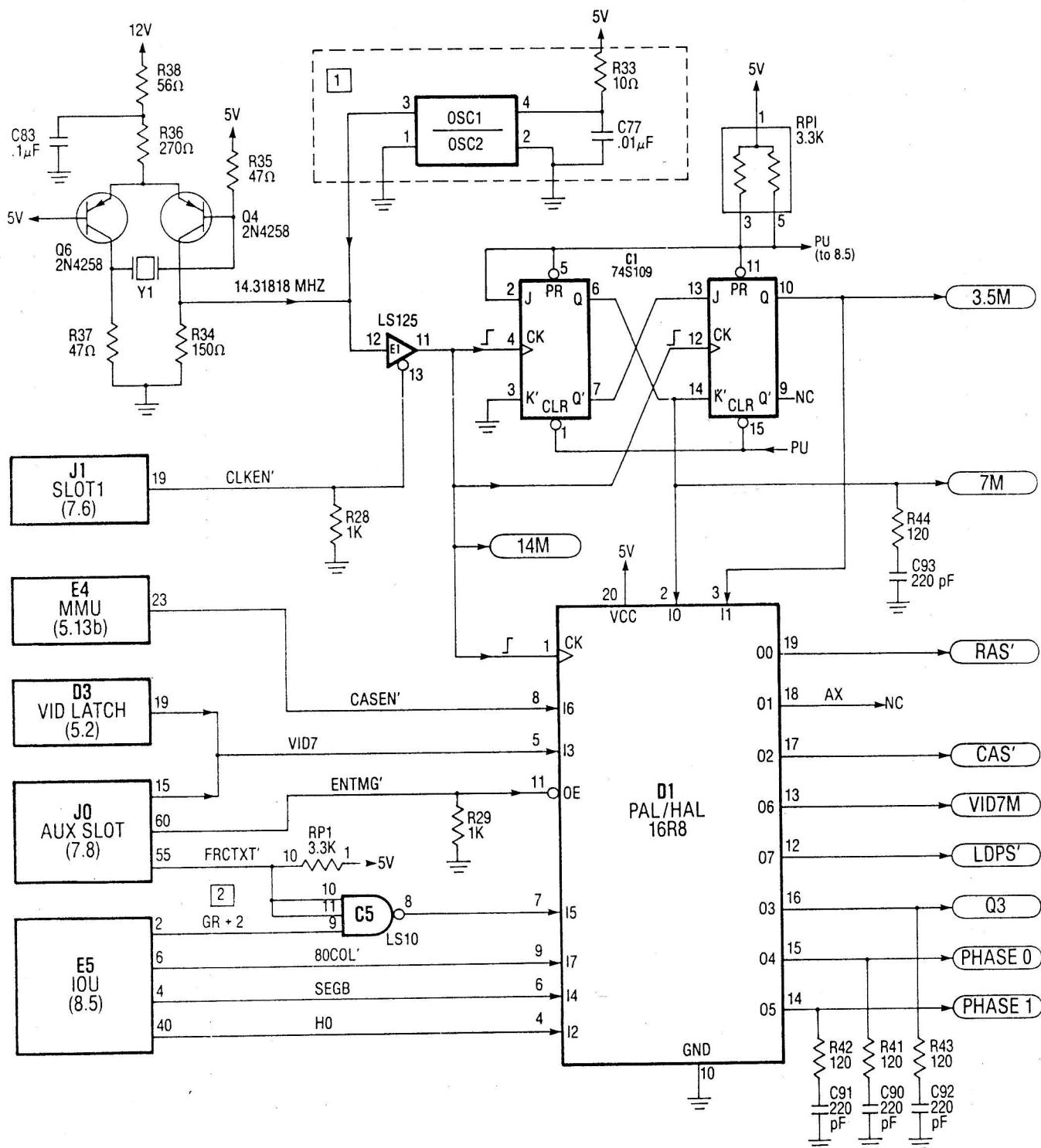

| Die Hardware des Taktgenerators                                                                                                                                                                                                                                               | 58        |

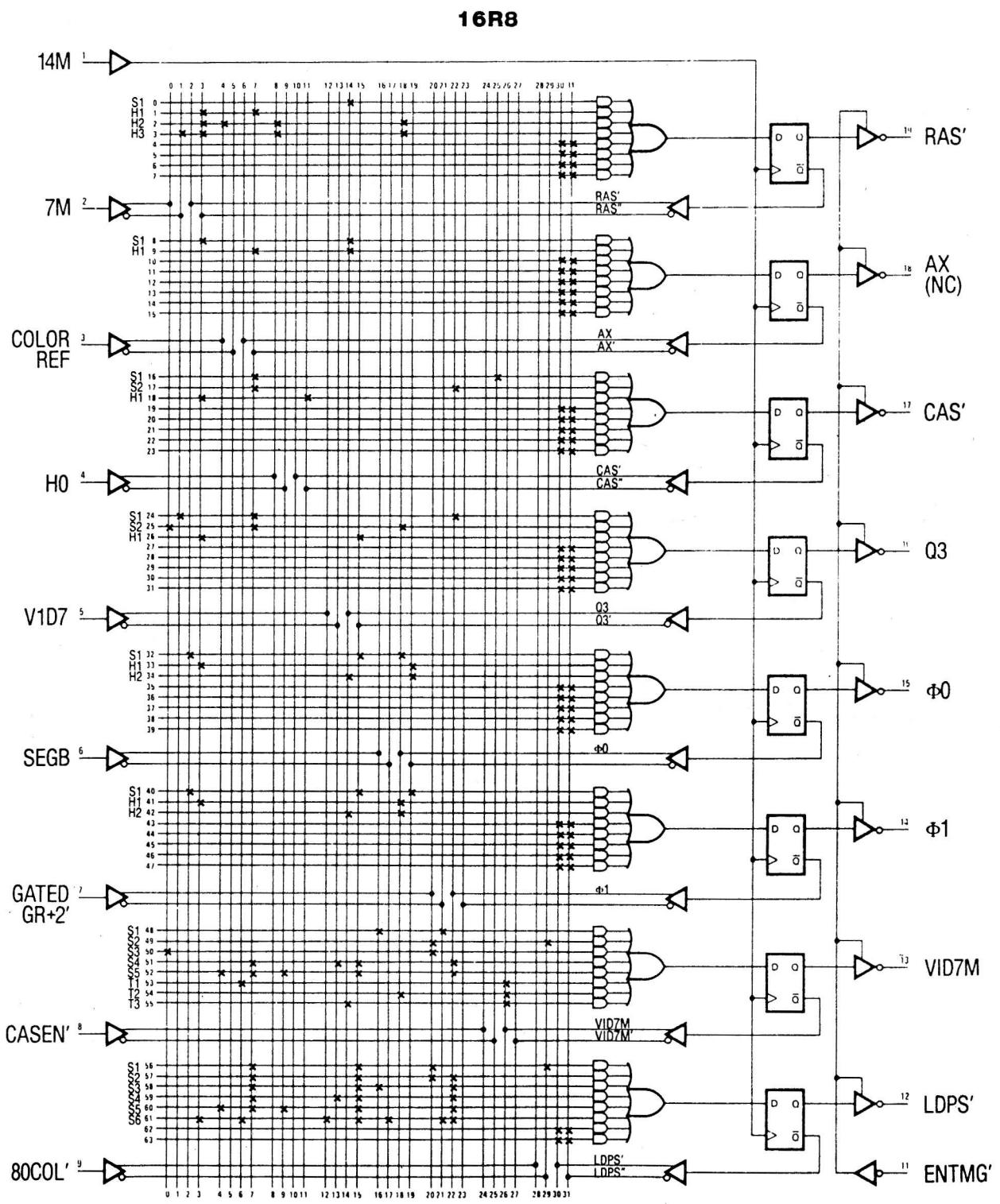

| Der HAL                                                                                                                                                                                                                                                                       | 60        |

| <b>Kapitel 4 - Der Mikroprozessor 6502</b>                                                                                                                                                                                                                                    | <b>65</b> |

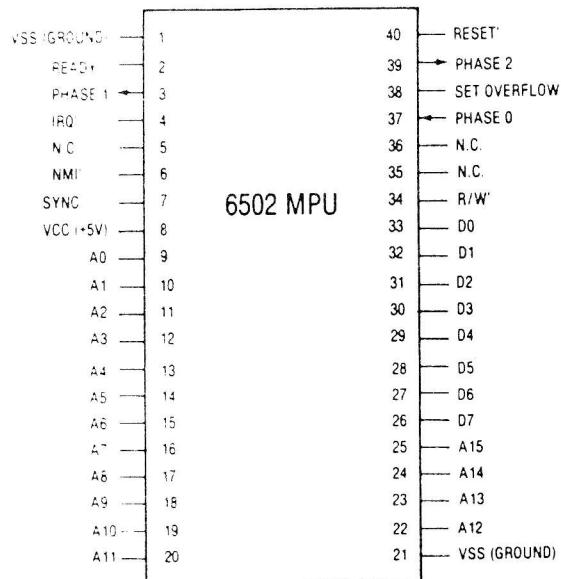

| Die Signale des 6502                                                                                                                                                                                                                                                          | 65        |

| <i>Taktsignale - PHASE0, PHASE1, PHASE2 65, Die Adreßausgänge und R/W' 66, Die Verbindung zum Datenbus 66, RESET' 66, Interrupts - IRQ' und NMI' 67, READY 67, SYNC 67, SET OVERFLOW' 68</i>                                                                                  |           |

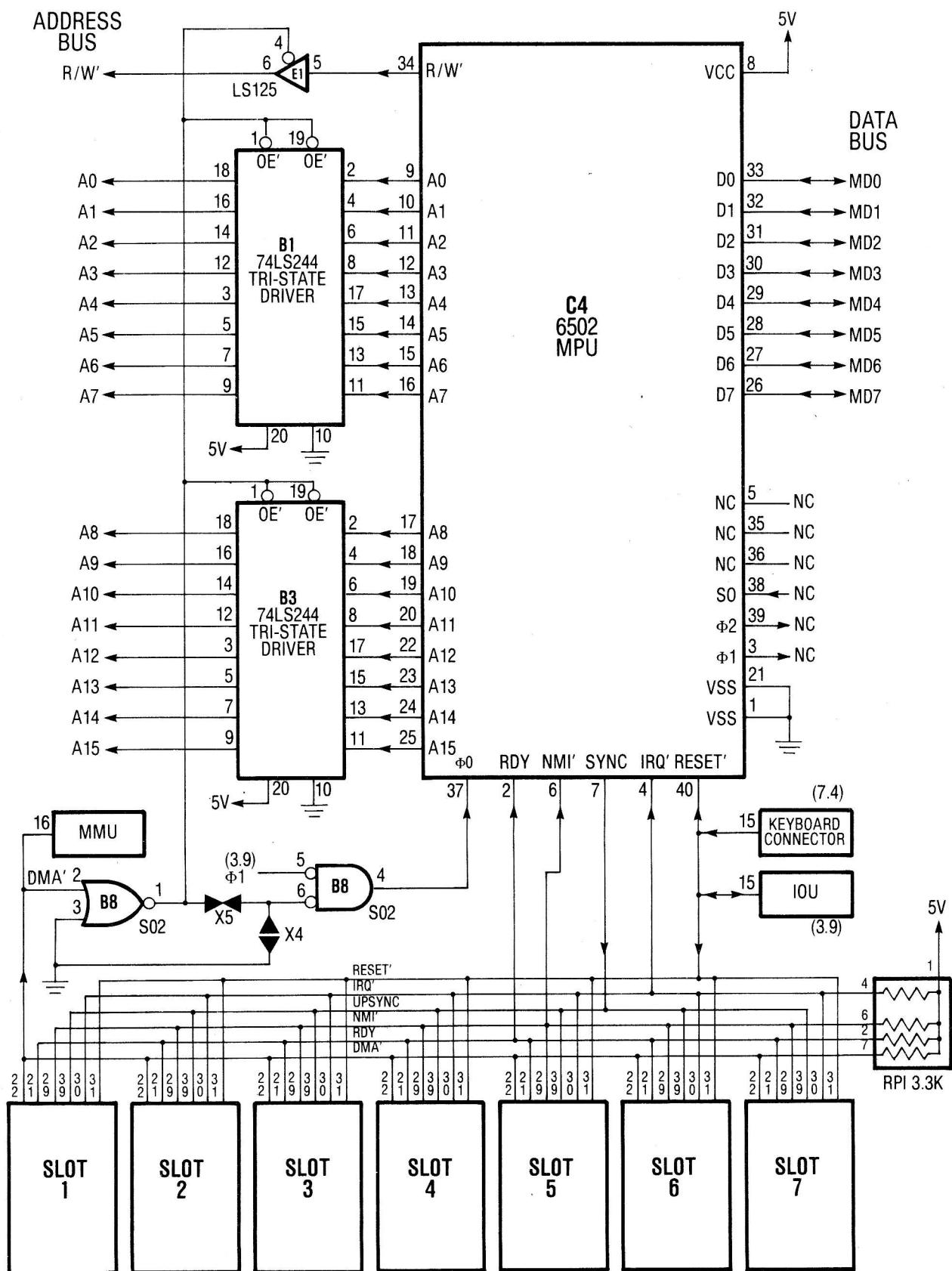

| Die Verbindungen des 6502 im Apple //e                                                                                                                                                                                                                                        | 68        |

| Die Speicherbelegung des 6502                                                                                                                                                                                                                                                 | 70        |

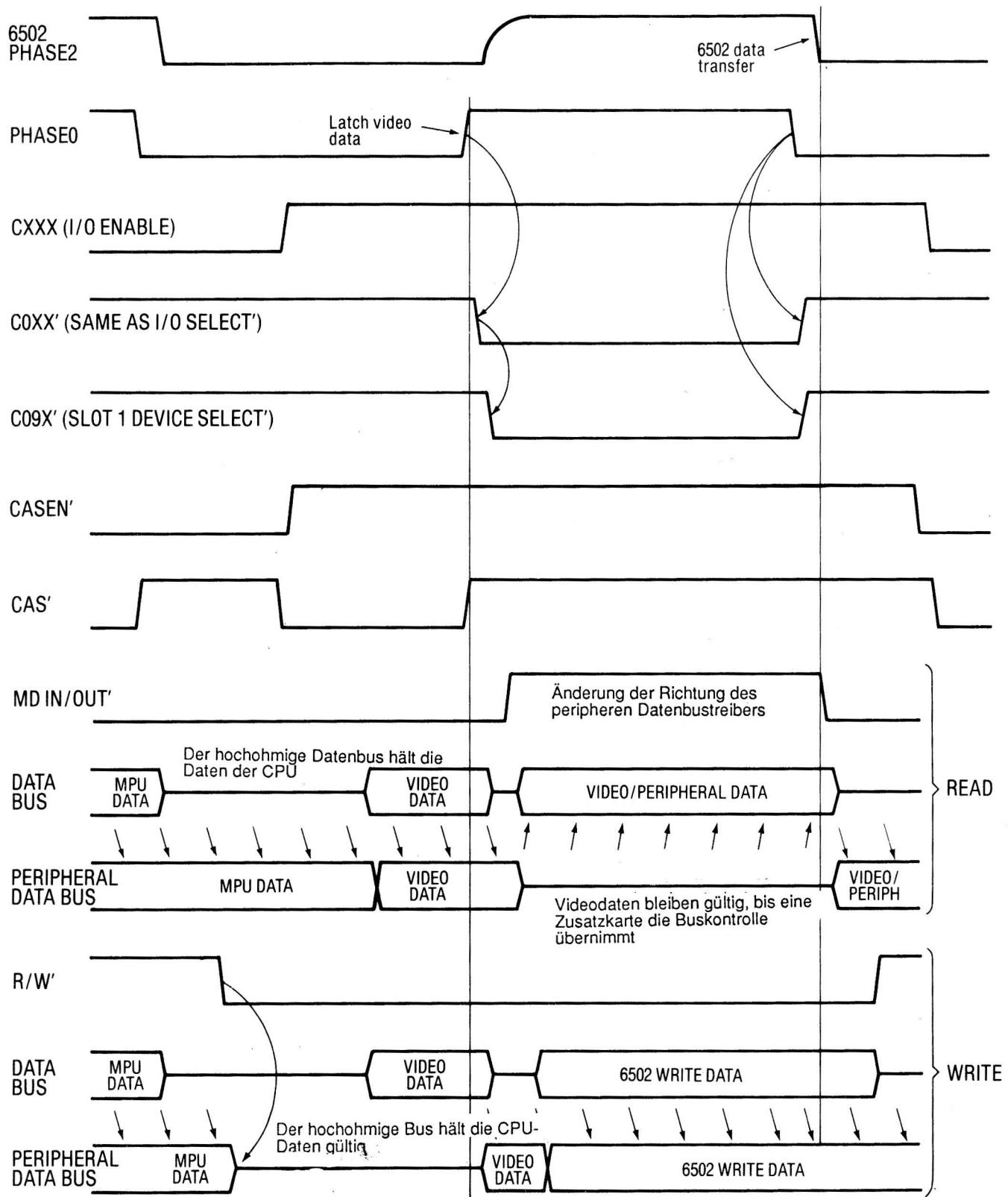

| Die Zeitsteuerung des 6502 im Apple //e                                                                                                                                                                                                                                       | 71        |

| Die Programmierung des Apple                                                                                                                                                                                                                                                  | 75        |

| DMA im Apple //e                                                                                                                                                                                                                                                              | 78        |

| 6502-Interrupts im Apple //e                                                                                                                                                                                                                                                  | 82        |

| <i>RESET' 82, NMI' und IRQ' 83, Der Befehl BRK 86, Die Behandlung von IRQ' und BRK im verbesserten Apple //e 87, Die Rangfolge der Interrupts 89</i>                                                                                                                          |           |

| Der Mikroprozessor 65C02                                                                                                                                                                                                                                                      | 90        |

| Befehlsübersicht und Unterschiede zwischen 6502 und 65C02                                                                                                                                                                                                                     | 92        |

|                                                                                         |            |

|-----------------------------------------------------------------------------------------|------------|

| <b>Kapitel 5 - RAM und die Verwaltung des Speichers</b>                                 | <b>99</b>  |

| Die dynamischen RAMs                                                                    | 99         |

| Die Verbindungen des RAMs im Apple //e                                                  | 101        |

| Die RAM-Adreßmultiplexer                                                                | 104        |

| <i>Die Adreßlogik des Videoscanners 106, Der Scan-Prozeß für TEXT und LoRes 109,</i>    |            |

| <i>Der Scan-Prozeß für HiRes 111, Der Scan-Prozeß im Modus MIXED 113</i>                |            |

| Der RAM-Refresh im Apple //e                                                            | 119        |

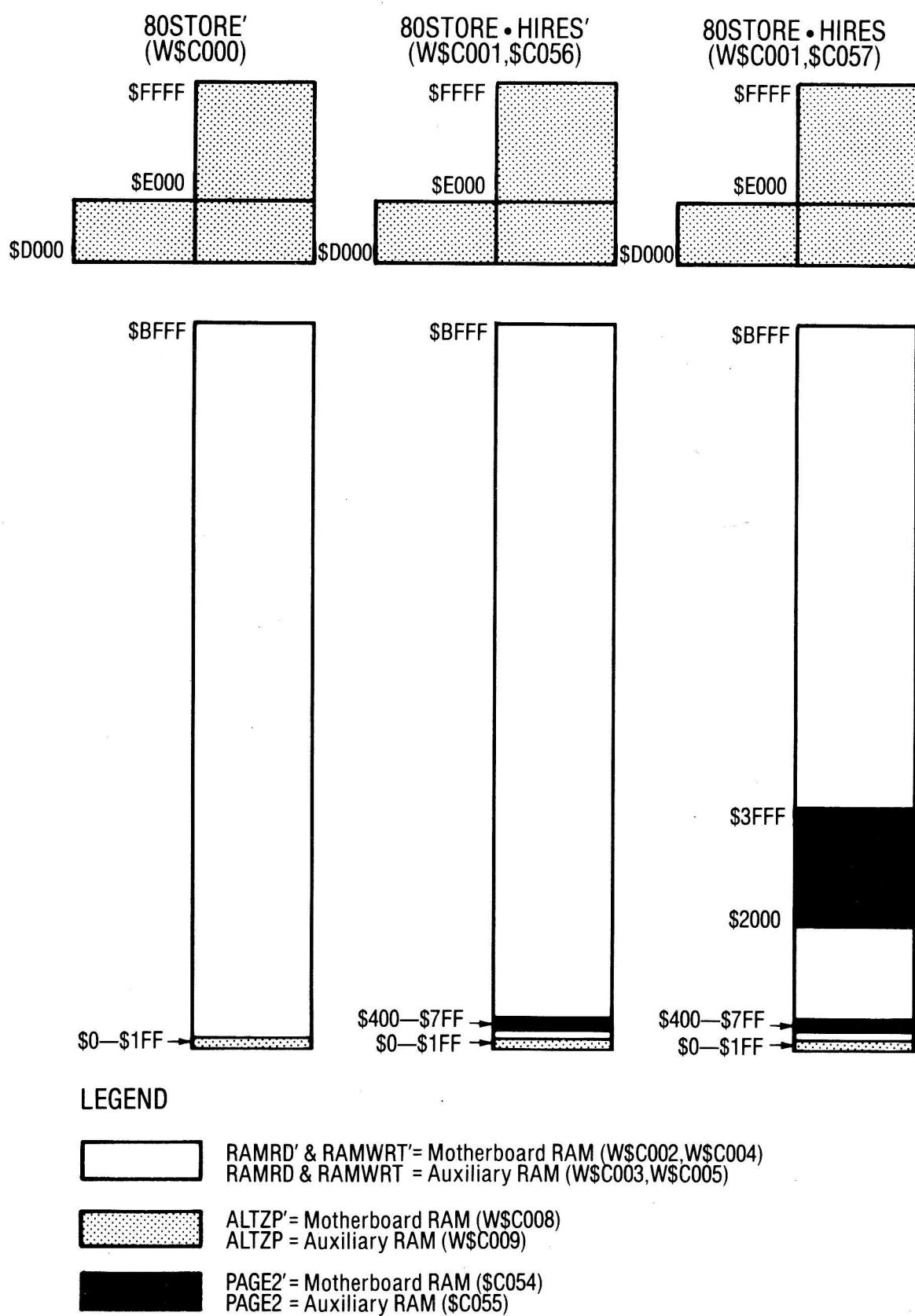

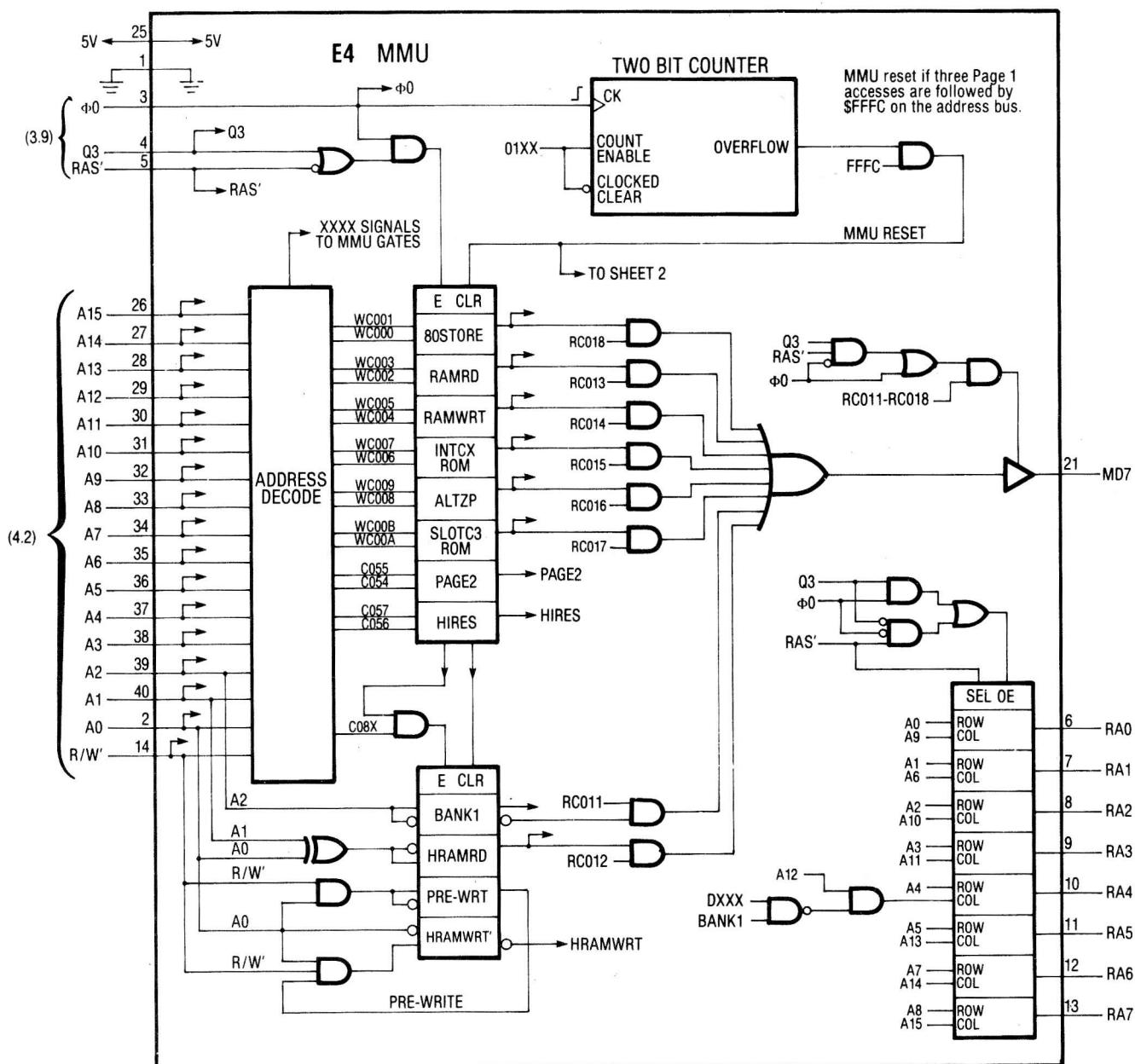

| Die Speicherverwaltung                                                                  | 120        |

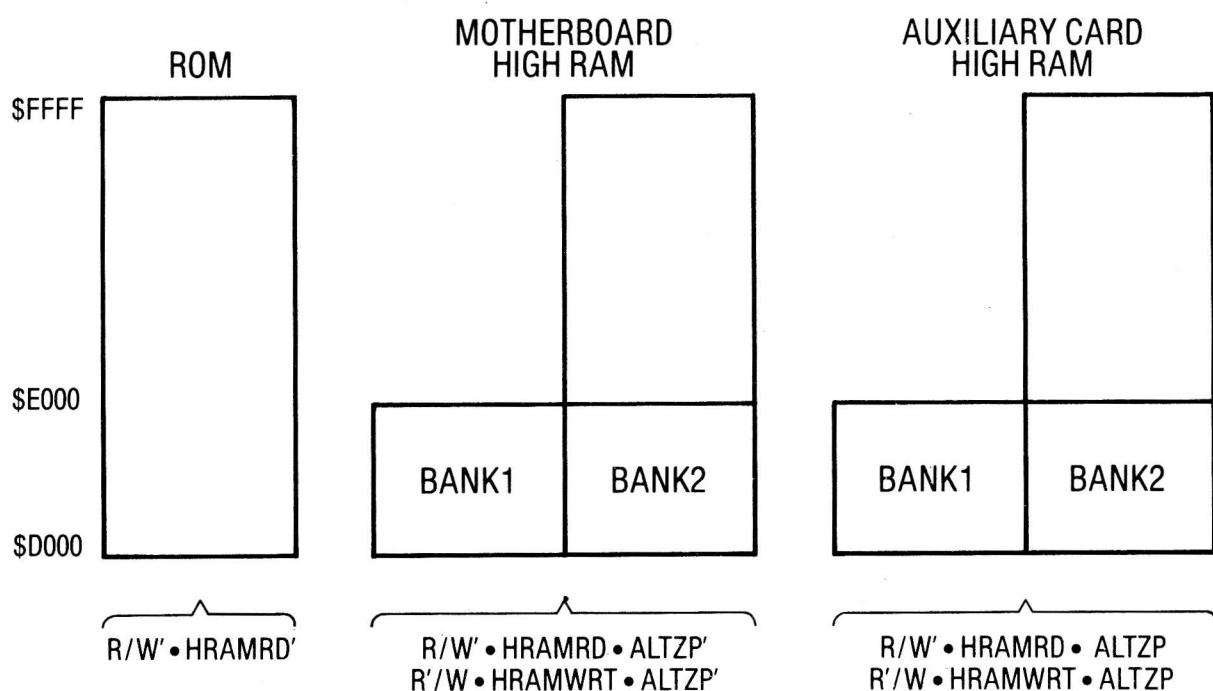

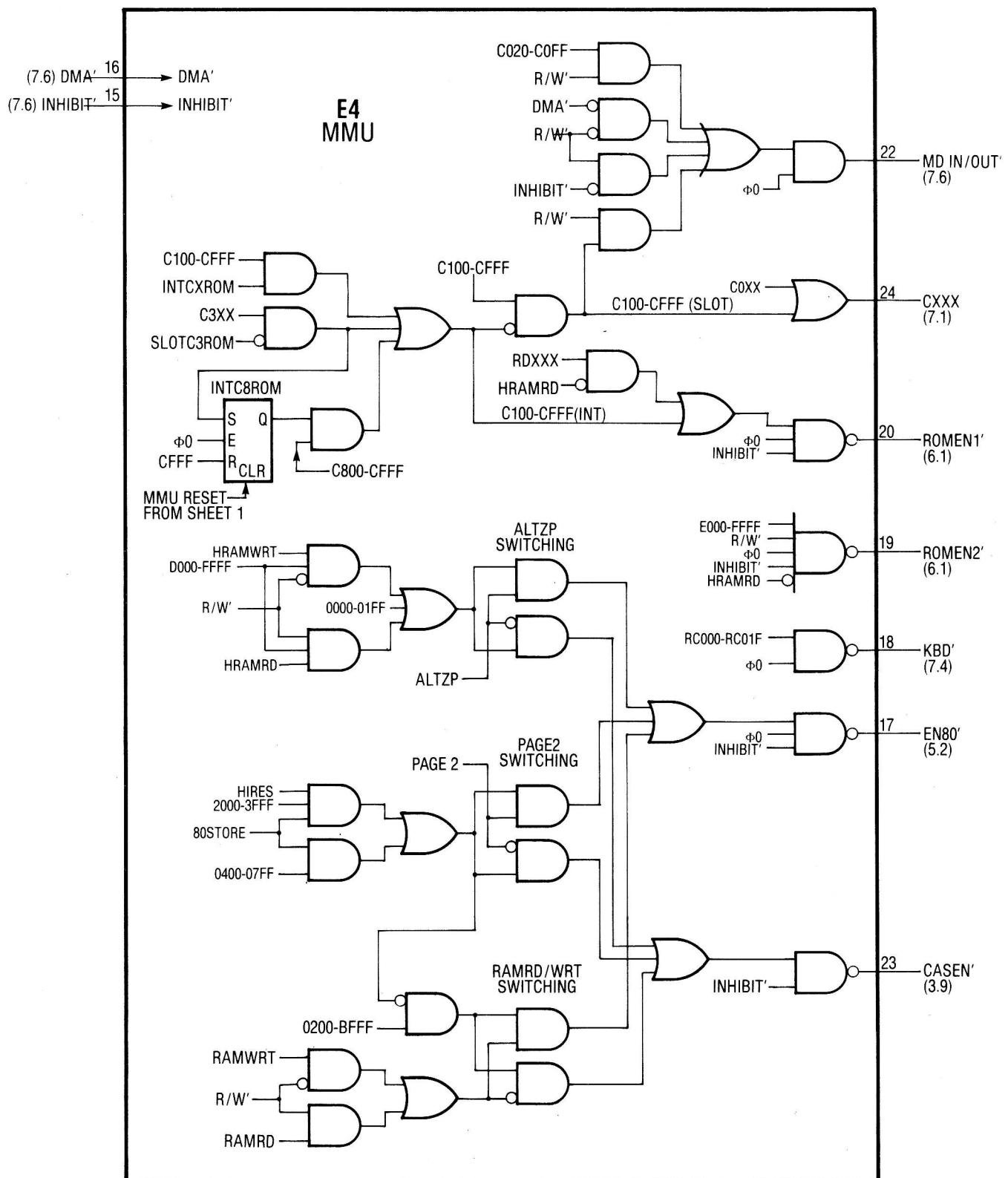

| <i>Die Softswitches der MMU 121, Die Schaltung des hohen RAMs (\$D000-\$FFFF) 123,</i>  |            |

| <i>Die Schaltung zwischen dem RAM der Hauptplatine und dem AUX-RAM 127,</i>             |            |

| <i>Der Aufbau des I/O-Bereichs (\$C000-\$CFFF) 129, KBD' und MD IN/OUT' 130,</i>        |            |

| <i>Der funktionale Aufbau der MMU 131, Laufzeiten in der MMU 135</i>                    |            |

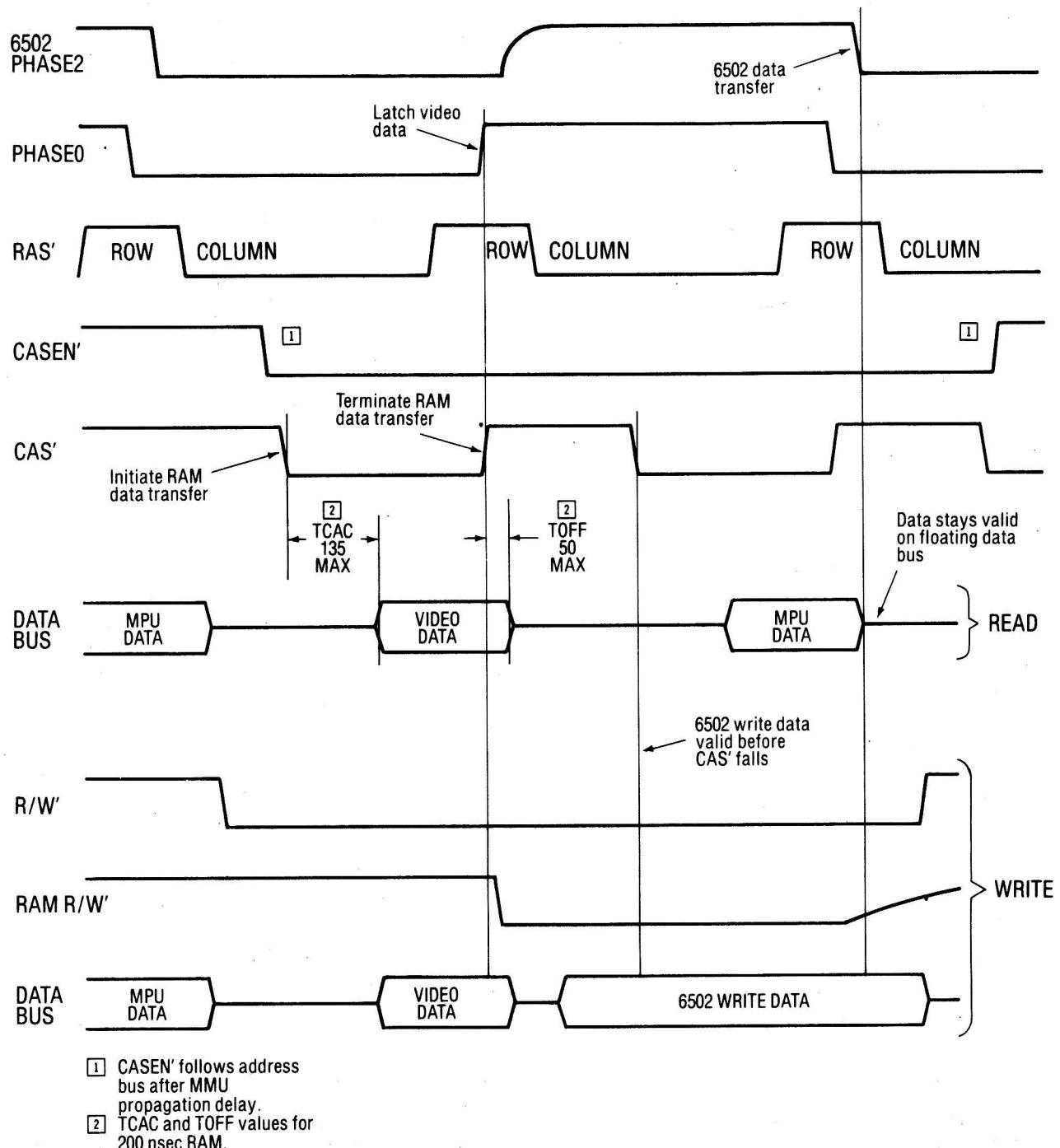

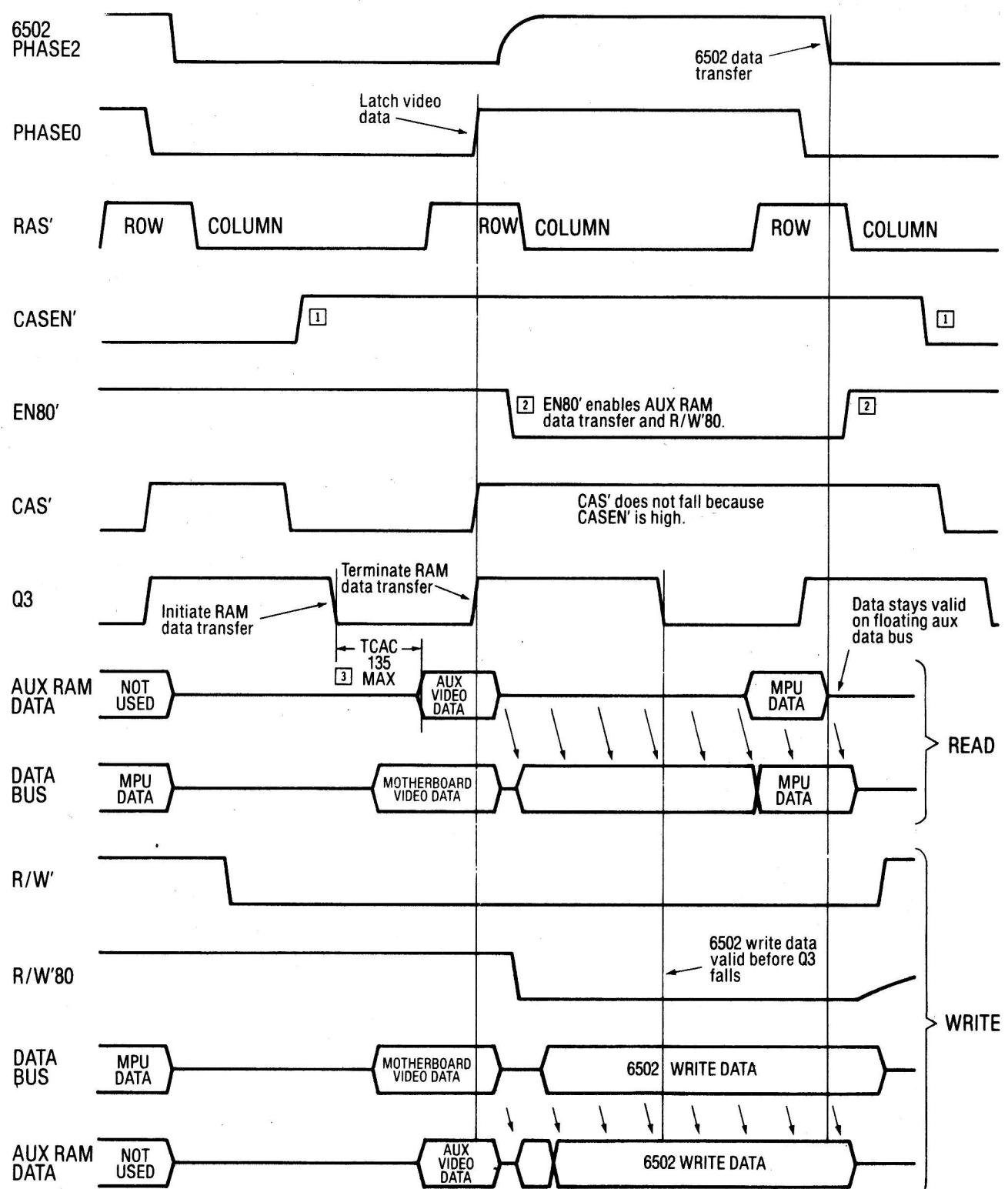

| Das "Timing" des RAMs im Apple //e                                                      | 136        |

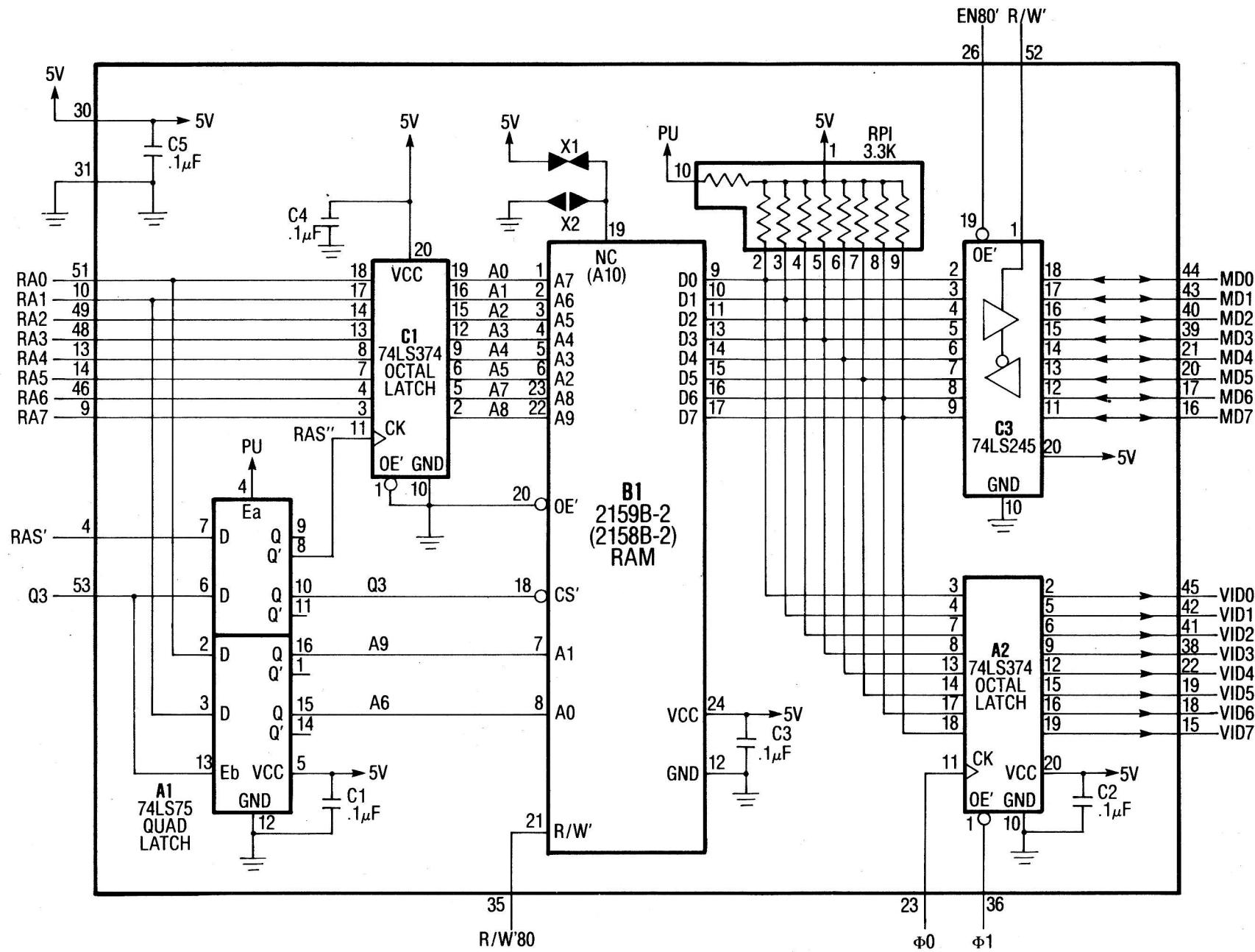

| Die 80-Zeichen-Karte mit 1 kByte RAM                                                    | 140        |

| <b>Kapitel 6 - ROM im Apple //e</b>                                                     | <b>143</b> |

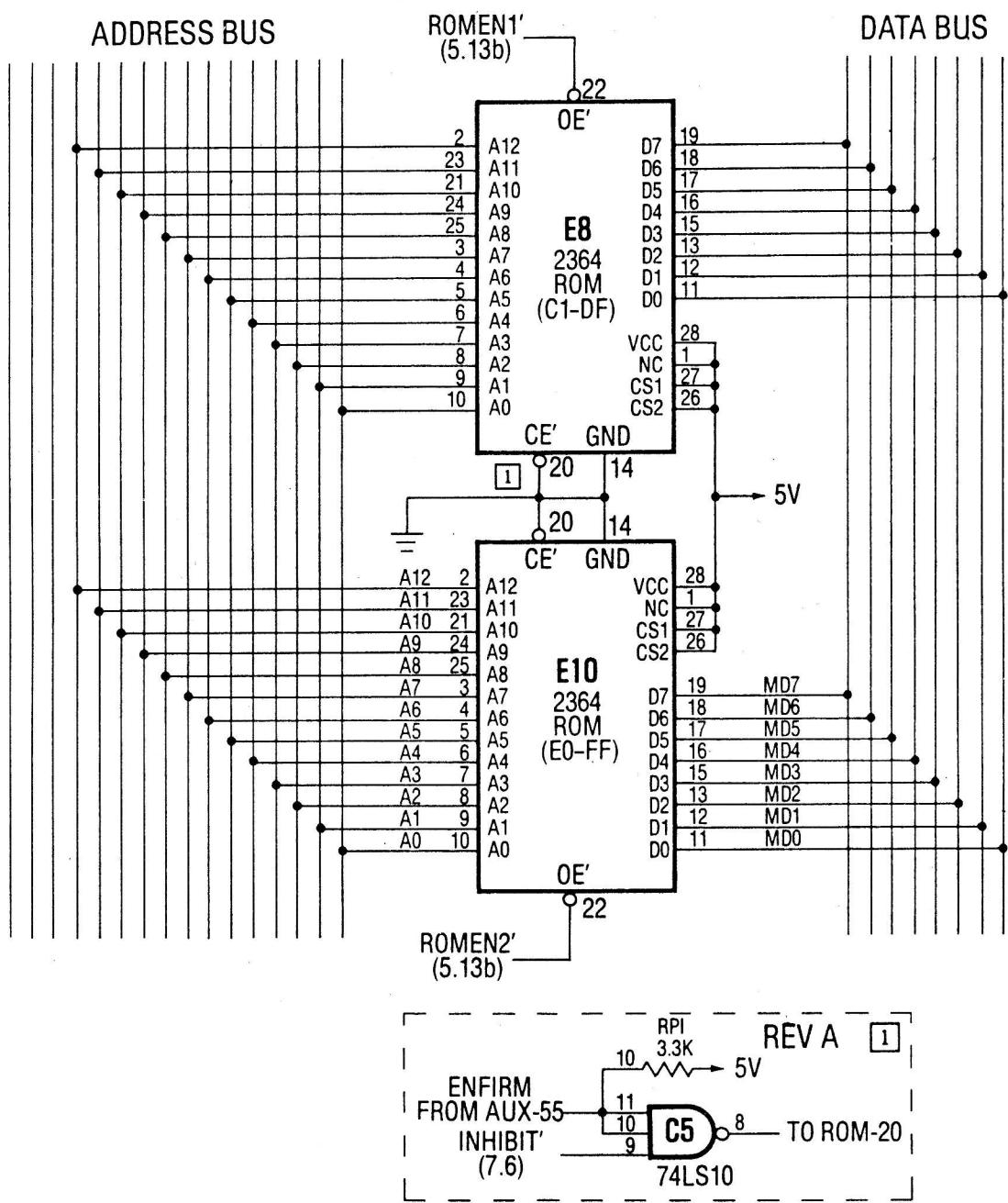

| ROM-Hardware                                                                            | 143        |

| ROMEN1' und ROMEN2'                                                                     | 144        |

| ROM in den Steckplätzen                                                                 | 146        |

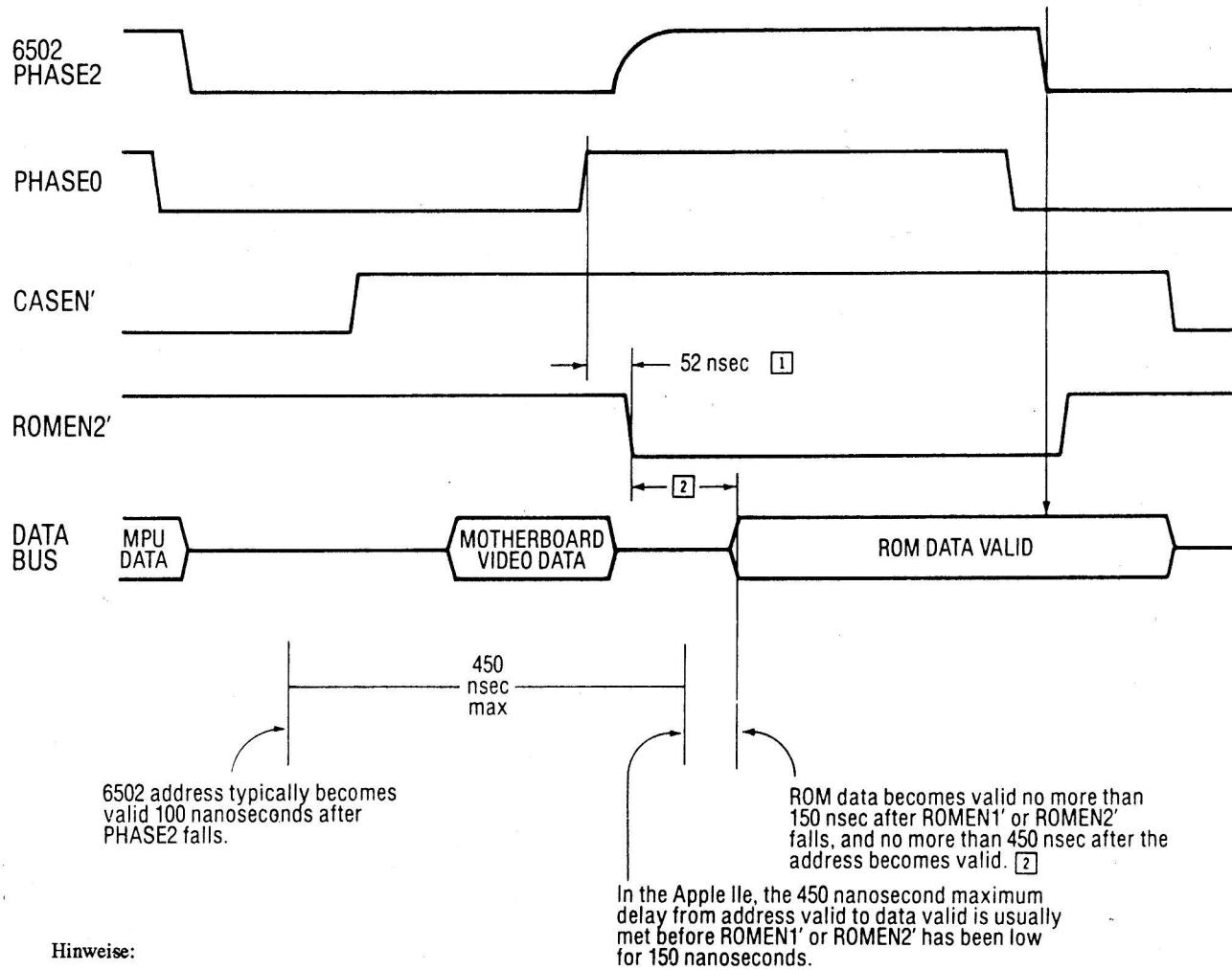

| Das Zeitverhalten der ROMs                                                              | 147        |

| Die Firmware des Apple                                                                  | 148        |

| <i>Das Monitorprogramm 149, Der Apple II+ 150, Der Einfluß der 16k-Sprachkarte 150,</i> |            |

| <i>Der Apple //e 151</i>                                                                |            |

| Der verbesserte Apple //e                                                               | 152        |

| <b>Kapitel 7 - Ein-/Ausgabe im Apple //e</b>                                            | <b>153</b> |

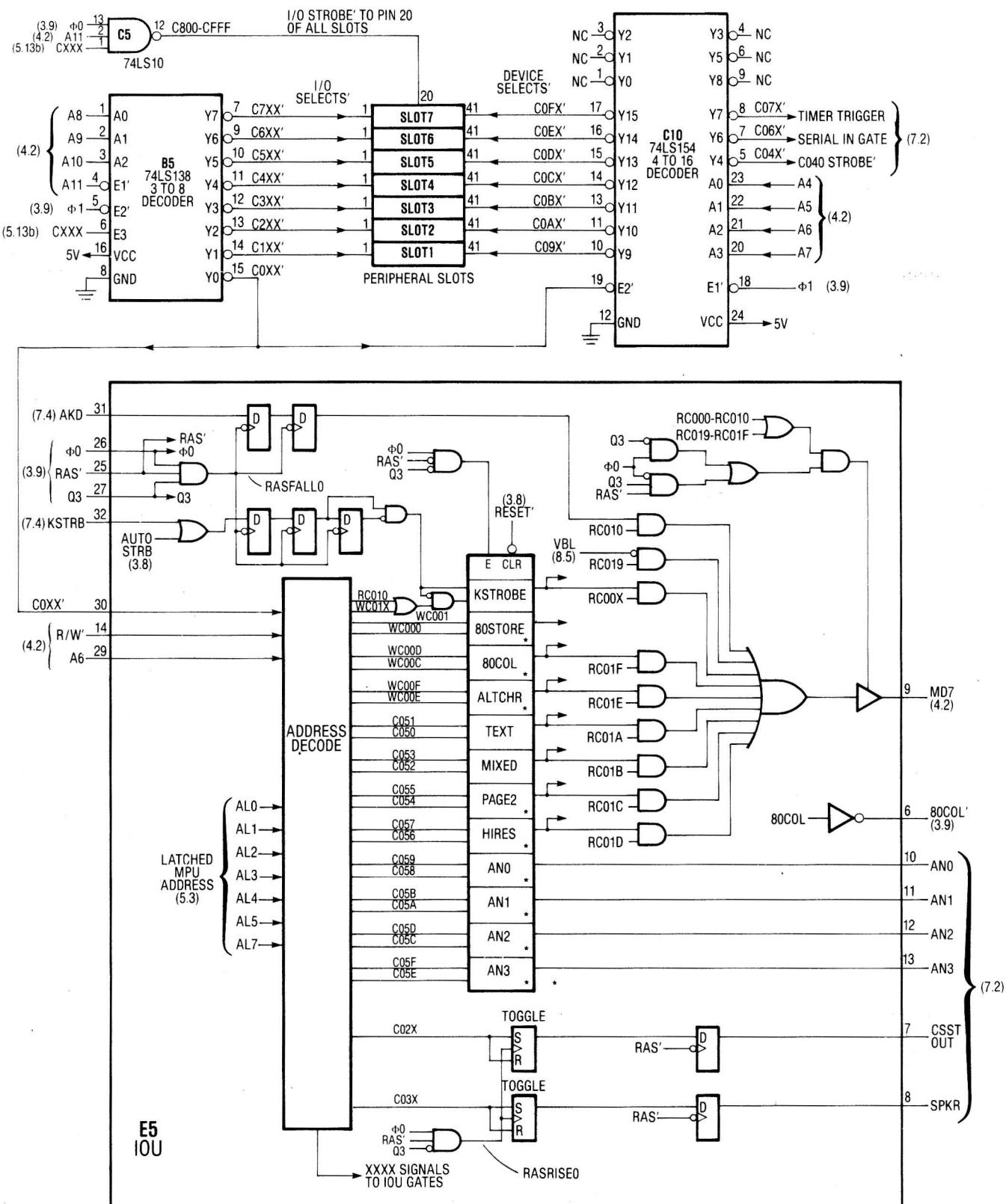

| Die Dekodierung der Peripherieadressen                                                  | 153        |

| Die Softswitches der IOU                                                                | 155        |

| Der Aufbau des seriellen I/O                                                            | 158        |

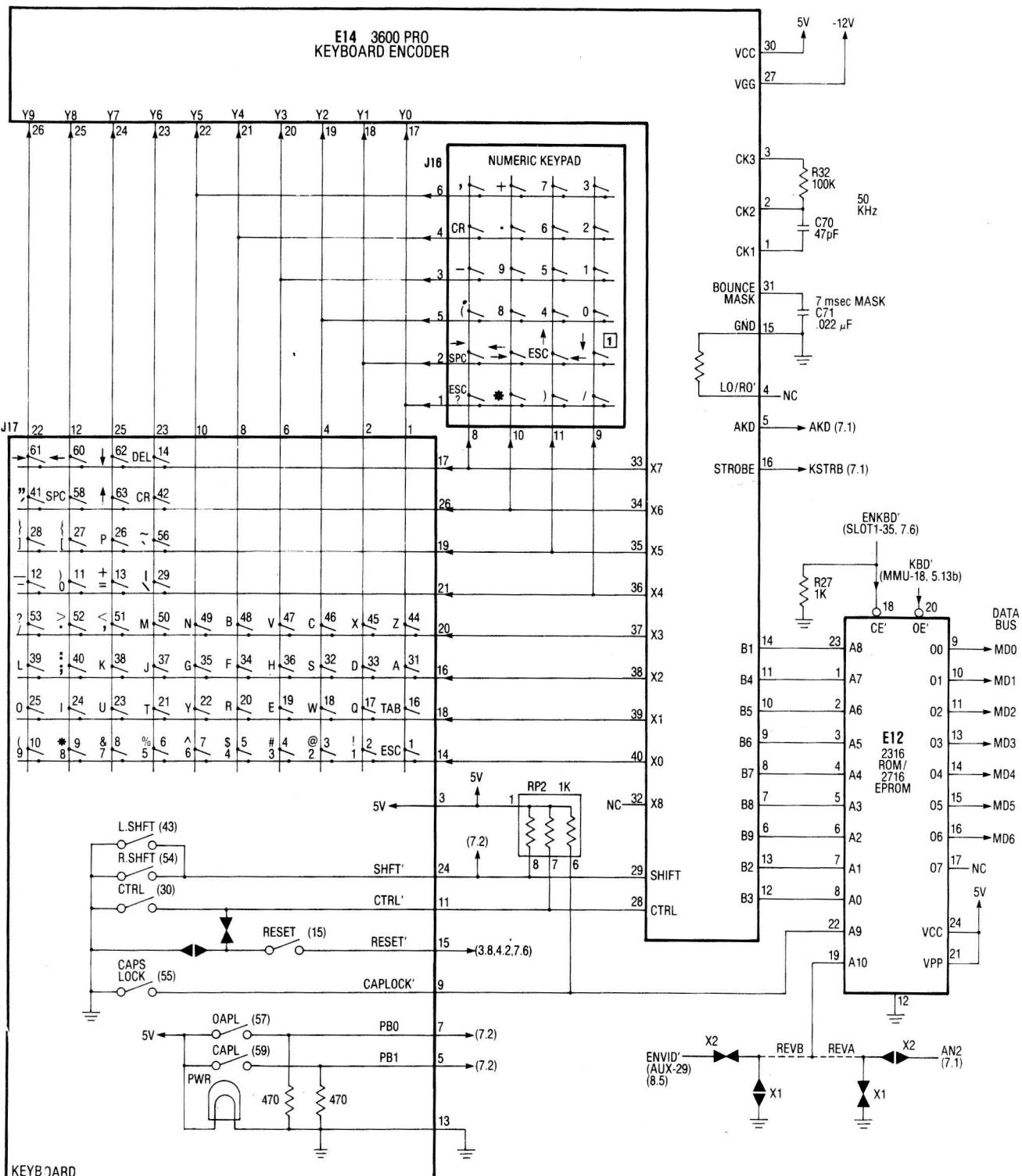

| Die Tastatur des Apple //e                                                              | 162        |

| <i>Zusammenfassung der funktionellen Eigenschaften der Tastatur 167,</i>                |            |

| <i>Das I/O STROBE'-Protokoll 174</i>                                                    |            |

| Die Struktur der Ein-/Ausgabe                                                           |            |

| <i>KSW und CSW 175, I/O und der Monitor des Apple 175, Die Umleitung des I/O</i>        |            |

| <i>zu anderen Geräten 176, Peripherie Zusatzkarten und primäre I/O-Geräte 177</i>       |            |

| Die Zeitableüfe des I/O                                                                 | 178        |

| Der spezielle Steckplatz                                                                | 181        |

| <b>Kapitel 8 - Der Videogenerator</b>                                                   | <b>185</b> |

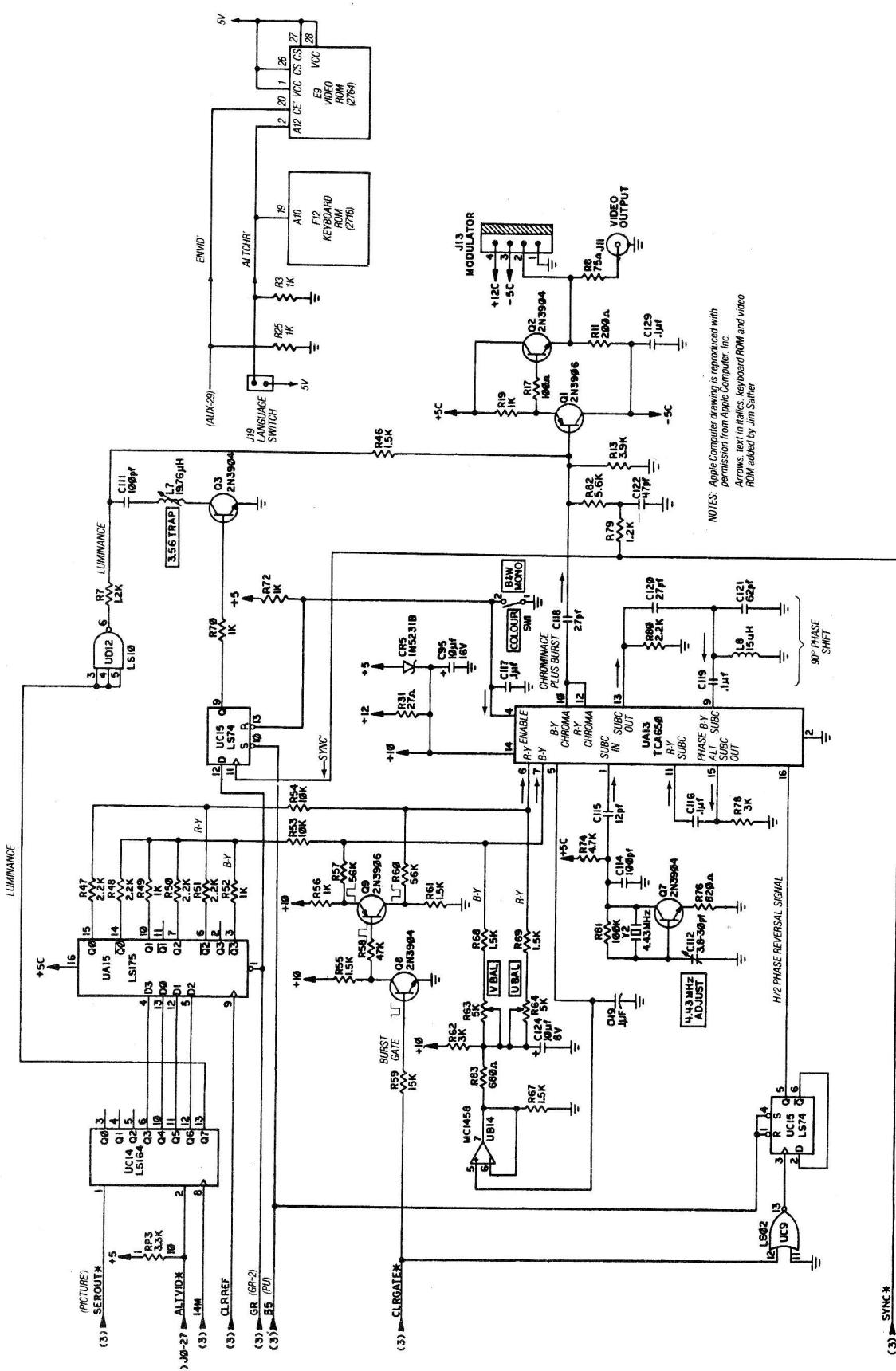

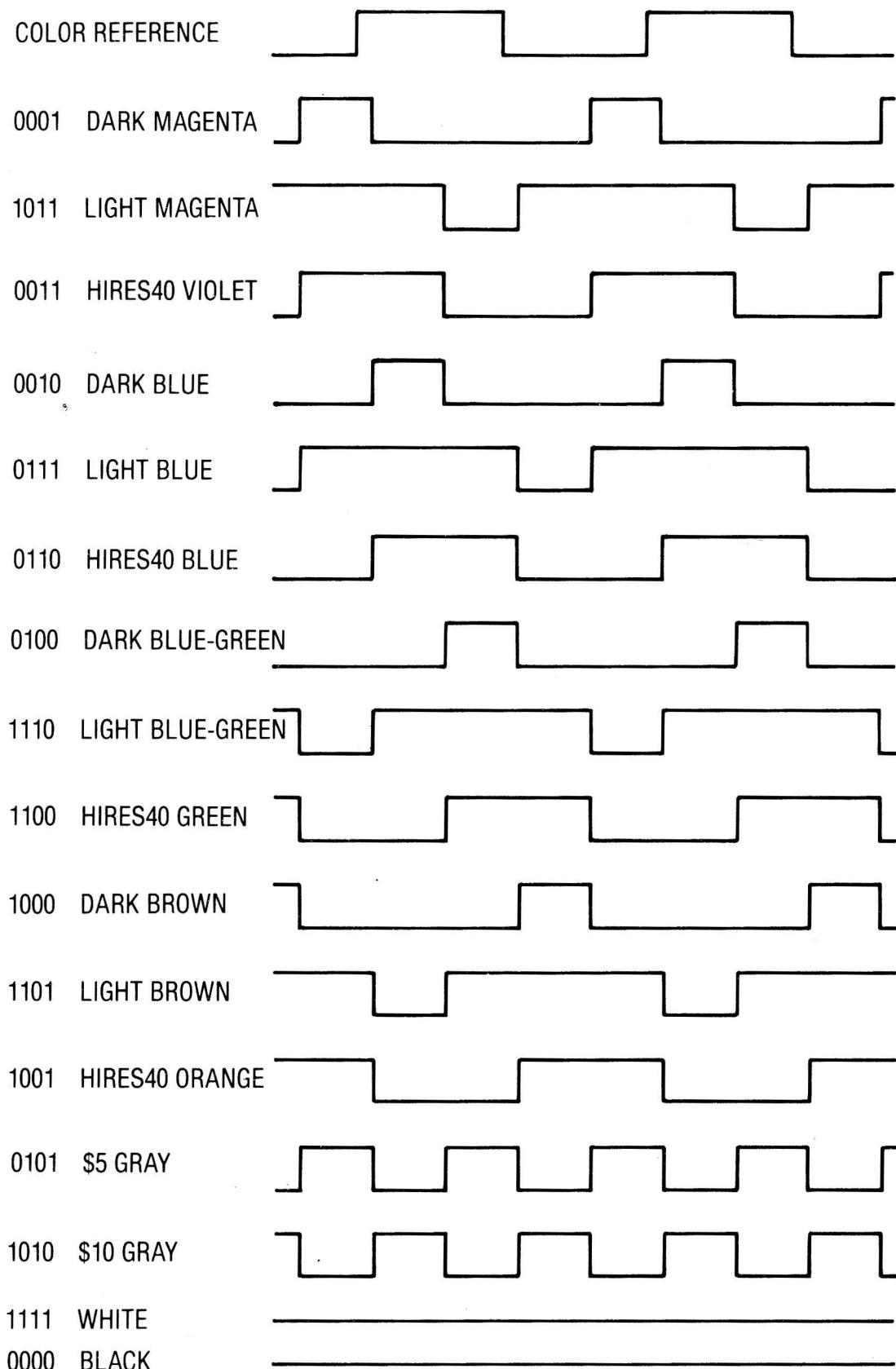

| Farbsignale                                                                             | 190        |

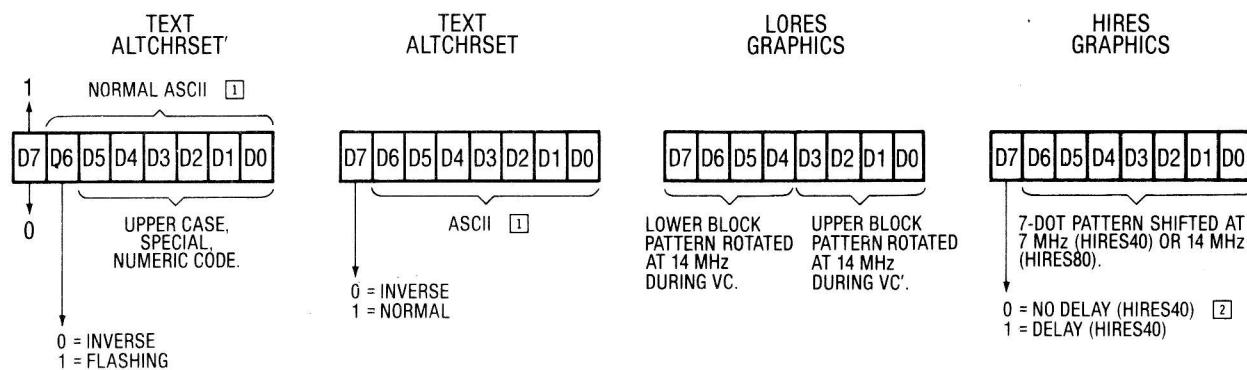

| Die Repräsentation der Bildinformation im Speicher                                      | 192        |

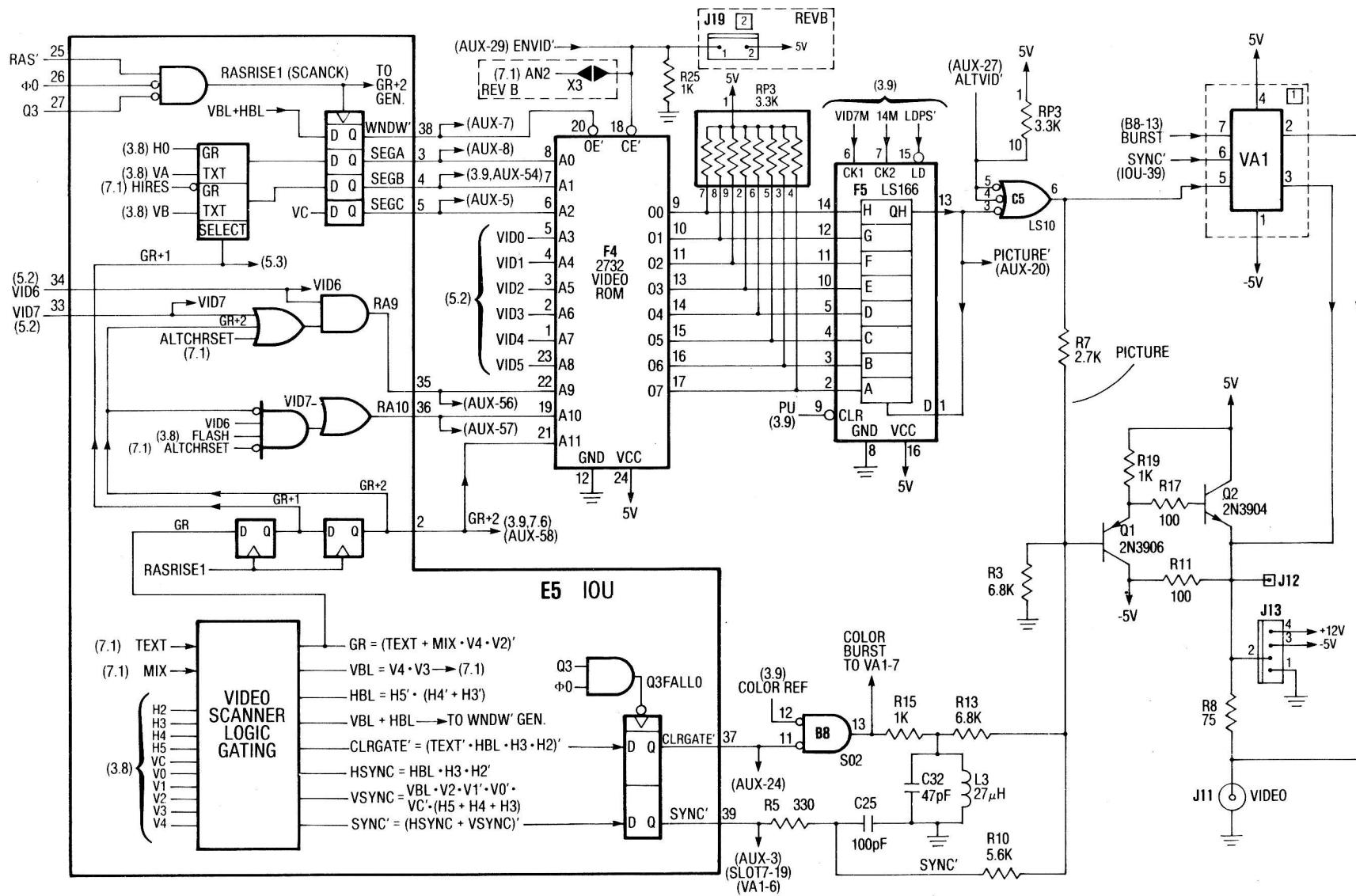

| Die Hardware des Videogenerators                                                        | 194        |

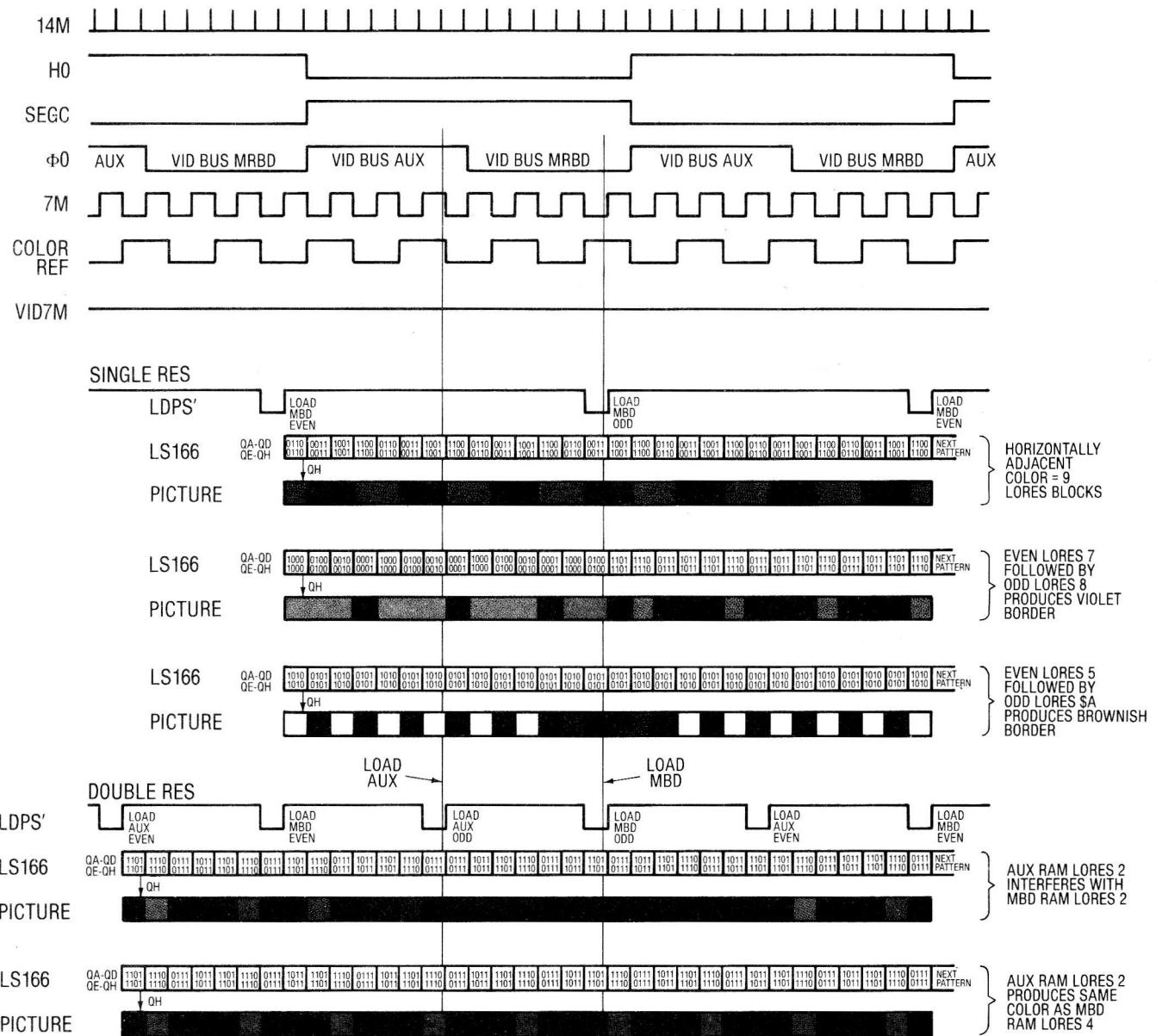

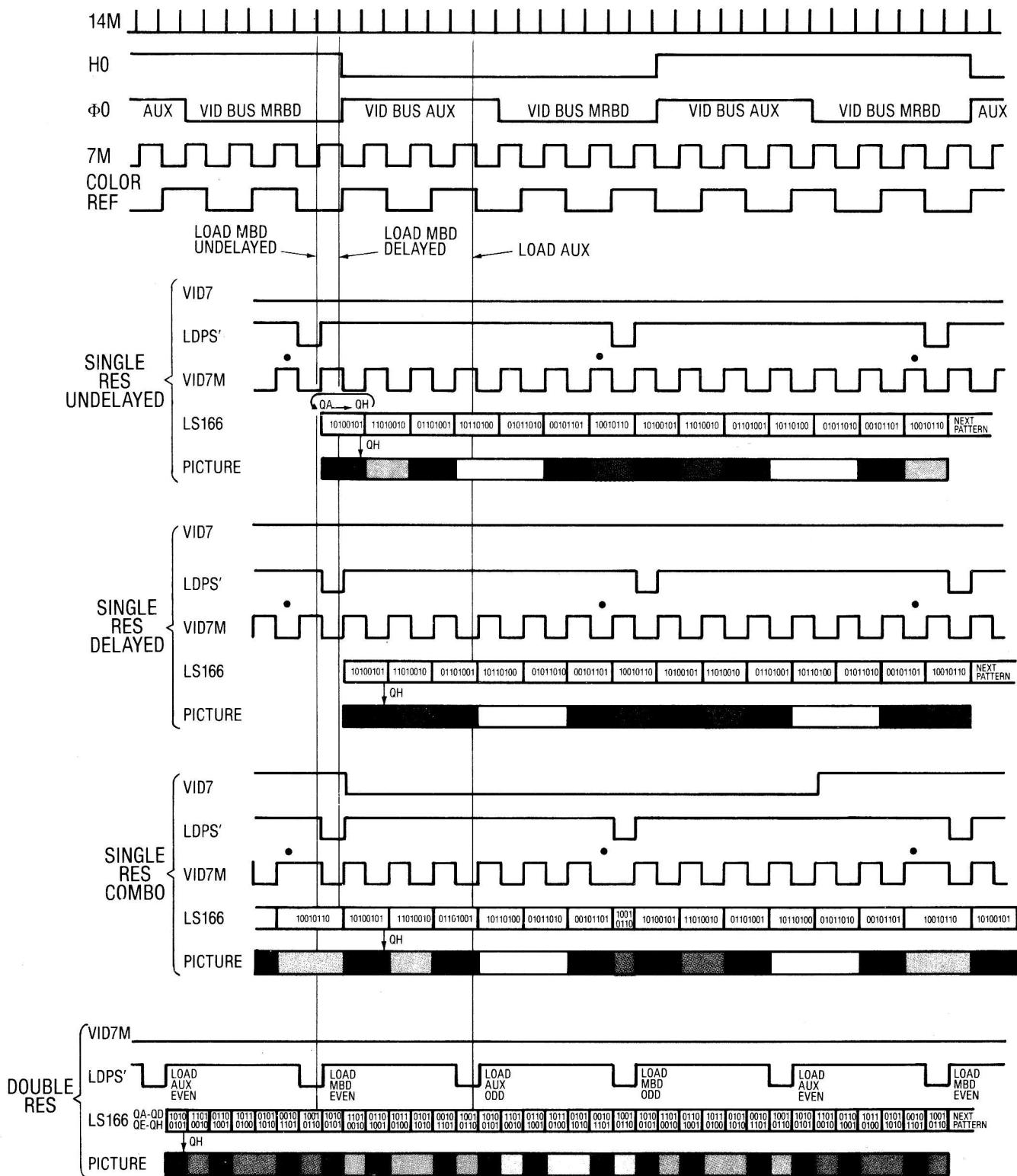

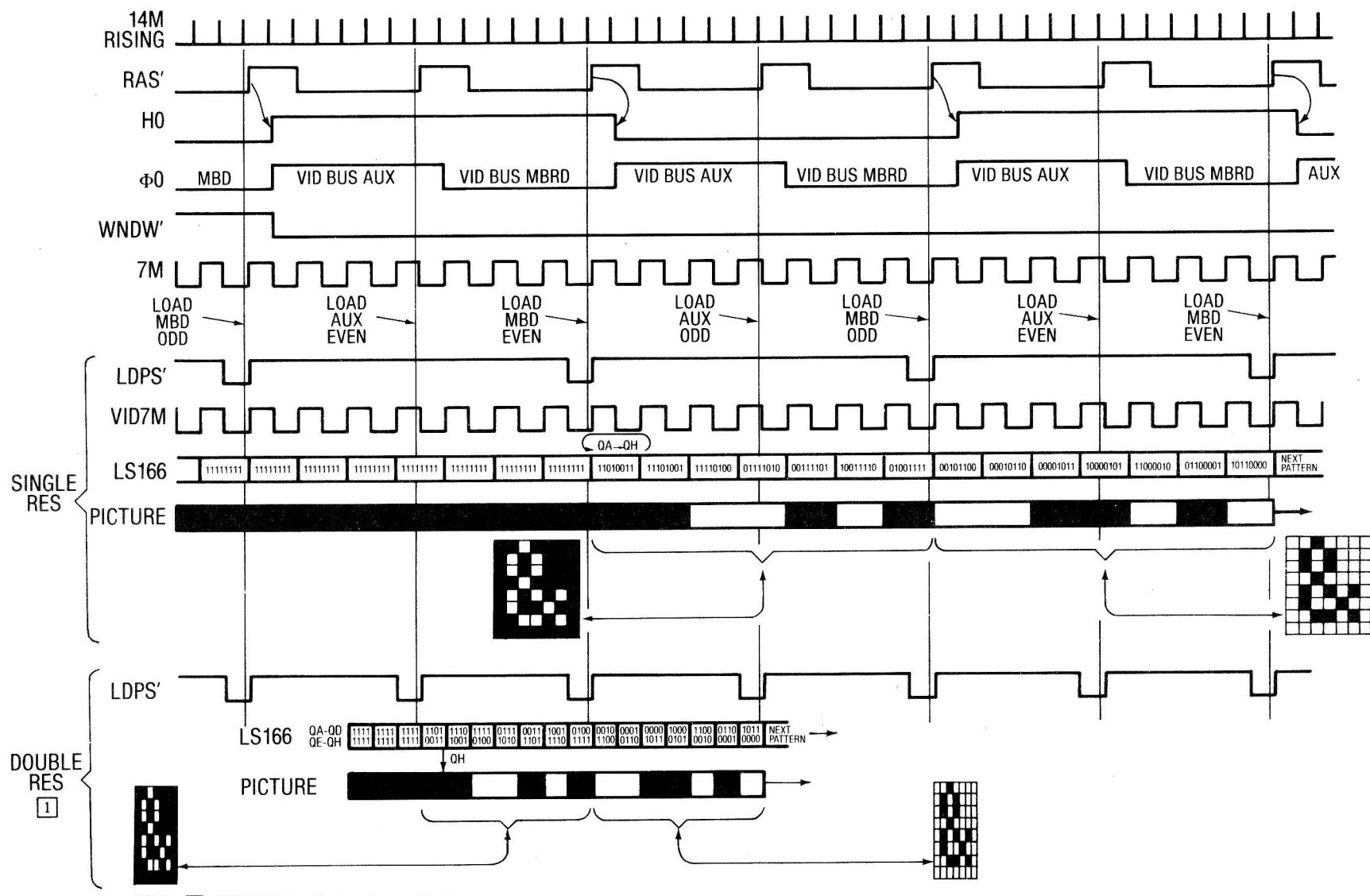

| <i>Die Eingänge des Video-ROMs 196, Laden und Schieben von Bitmustern 200,</i>          |            |

| <i>Die Videoausgabe im europäischen Apple //e 202</i>                                   |            |

| Die Softswitches für den Videomodus                                                     | 206        |

| Die Zeitsignale der Bilderzeugung                                                       | 210        |

| Die Ausgabe von TEXT                                                                    | 214        |

| Die Erzeugung und Ausgabe von LoRes-Grafik                                              | 217        |

| <i>Die Ausgabe von LoRes40 218, Die Ausgabe von LoRes80 220</i>                         |            |

| Die Erzeugung und Ausgabe von HiRes-Grafik                                              | 222        |

| Die Ausgabe von HiRes40                                                                 | 222        |

| <i>Die Ausgabe von HiRes80 226</i>                                                      |            |

| Die Umschaltungen im Modus MIXED                                                        | 228        |

# Kapitel 1

## Der Apple //e - ein Überblick

Der folgende Überblick ist ein kurz gehaltener Abriss der Hardware des Apple //e. Er ist nicht als Beschreibung dessen gedacht, was man mit einem ausgefuchsten Programm und dem //e alles anstellen kann, sondern mehr als Beschreibung der grundlegenden Möglichkeiten, die dem Programmierer (und dem Entwurfsingenieur für Zusatzkarten) zur Verfügung stehen. Wir beginnen mit einer Einführung über Mikrocomputer im allgemeinen und einer Definition der dazugehörigen Terminologie. Leser, die gerade erst begonnen haben, sich mit den elektronischen Innereien ihres Computers zu beschäftigen, sollten sich durch die nun folgende Informationsflut nicht entmutigen lassen. Es ist auch nicht nötig, alle hier vorgestellten Punkte bis ins letzte Detail zu verstehen - die folgenden Kapitel stellen eine starke Erweiterung der einzelnen Oberpunkte dar und haben dabei auch mehr Raum für Erklärungen. Speziell Kapitel 2 beantwortet viele Fragen, die bei der Lektüre von Kapitel 1 auftauchen dürften.

Der Apple //e ist eine erweiterte und verbesserte Version des Apple II, der Mitte der siebziger Jahre von Steve Wozniak ("Woz") konstruiert wurde. Er entspricht einem Apple II mit einer 16k-Speichererweiterung in Steckplatz 0 und einer 80-Zeichen-Karte in Steckplatz 3. Dabei wurde besonderen Wert auf "Aufwärtskompatibilität" gelegt, d.h. Programme, die für den Apple II geschrieben wurden, laufen im allgemeinen auch auf einem //e - der //e bietet allerdings darüber hinaus noch einige zusätzliche Möglichkeiten. Die großen Unterschiede liegen in weiteren 64 kByte RAM, einer erweiterten Tastatur mit einigen zusätzlichen Tasten und der Möglichkeit, doppelt so hoch auflösende Grafik darzustellen wie sein Vorgänger. Außerdem enthält er noch eine ganze Reihe kleinerer Verbesserungen, die allerdings für den Programmierer zumeist von untergeordneter Bedeutung sind.

Der Grund für die Firma Apple, eine neue Version des Apple II auf den Markt zu bringen, liegt hauptsächlich in einer Reduzierung der Herstellungskosten (der //e enthält erheblich weniger Bauteile als der Apple II) sowie die Beseitigung einiger Mängel des Computers beim Einsatz als Textverarbeitungssystem. Man kann das Ergebnis ohne Übertreibung als gelungen bezeichnen: Apple hat mit dem //e eine echte Verbesserung des II bzw. II+ herausgebracht, die sich ziemlich nahtlos in die Apple II-Serie einfügt. Die folgenden Beschreibungen gelten hauptsächlich für den //e, sind in weiten Teilen aber auch für den II bzw. II+ gültig.

### Ein Abriss des Apple //

Der Apple //e besteht aus fünf physikalisch voneinander getrennten Einheiten: Gehäuse, Tastatur, Stromversorgung, Lautsprecher und Hauptplatine ("motherboard"). Lautsprecher, Stromversorgung und Tastatur können dabei als (notwendige!) Zusätze betrachtet werden - sie sind in dieser oder ähnlicher Form in jedem Computer vorhanden. Der eigentliche Apple //e besteht allein aus der Hauptplatine, deshalb wird er auch manchmal als "Einplatinencomputer" bezeichnet. Auf einer einzigen Platine befinden sich der Mikroprozessor, der Speicher, die Elektronik zur Erzeugung der Videosignale inklusive der Grafik, sieben Erweiterungssteckplätze, ein spezieller Steckplatz und die notwendigen Schaltkreise zur Kommunikation mit einer Reihe von "externen" Geräten wie der bereits erwähnten Tastatur, den Spielsteuerungen etc. Alle diese Funktionen sind Teil einer organisierten Struktur, in deren Zentrum sich der Mikroprozessor befindet.

### Der Mikroprozessor und die Busstruktur

Der *Mikroprozessor* ist die zentrale Einheit eines Computers, sozusagen das Gehirn der Maschine. Von außen sieht man ihm das nicht an - physikalisch ist ein Mikroprozessor nur ein schwarzer Käfer, allerdings einer mit 40 Anschläßen. Ein Mikroprozessor (oder auch *CPU* = Central Processing Unit - "zentrale Verarbeitungseinheit") enthält eine Vielzahl von elektronischen Schaltungen und ist in der Lage, Befehle aus einem angeschlossenen Speicher zu lesen und sie in entsprechende Aktionen umzusetzen. Ein Computer, dessen zentrale Verarbeitungseinheit aus einem Mikroprozessor, d.h. aus einem einzigen Baustein besteht, wird als *Mikrocomputer* bezeichnet - im Unterschied zu Computern, bei denen diese CPU aus einem ganzen Satz von Chips besteht.

Der Apple //e verwendet einen Mikroprozessor des Typs 6502 (in den neueren Ausgaben des //e: 65C02). Dieser Chip hat 40 Pins ("Beinchen") und befindet sich ziemlich genau in der Mitte der Hauptplatine.

Jeder (digitale) Computer benötigt einen *Takt* ("Clock"), um einzelne Operationen miteinander zu synchronisieren. Das funktioniert ähnlich wie der Taktenschlag in der Musik - allerdings geht das bei Mikroprozessoren erheblich rascher: der Apple benutzt etwas mehr als eine Million Takte pro Sekunde. Im Vergleich zu anderen modernen Mikrocomputern ist sogar das noch recht wenig: selbst den 6502 gibt es mittlerweile in einer Ausgabe, die mit 4 Megahertz (4 Millionen Taktschlägen pro Sekunde) arbeitet, andere Prozessoren arbeiten mit noch höheren Taktraten (bis zu 12 Megahertz). Ein allgemeiner Rückschluß der Art "je schneller die Taktfrequenz, desto schneller der Prozessor" ist nicht unbedingt richtig, weil verschiedene Arten von Mikroprozessoren unterschiedliche Anzahlen von Taktschlägen für die Ausführung eines Befehls benötigen. Richtig ist allerdings die Aussage, daß ein 6502 mit 2 Megahertz Taktfrequenz genau doppelt so schnell arbeitet wie mit einem Megahertz.

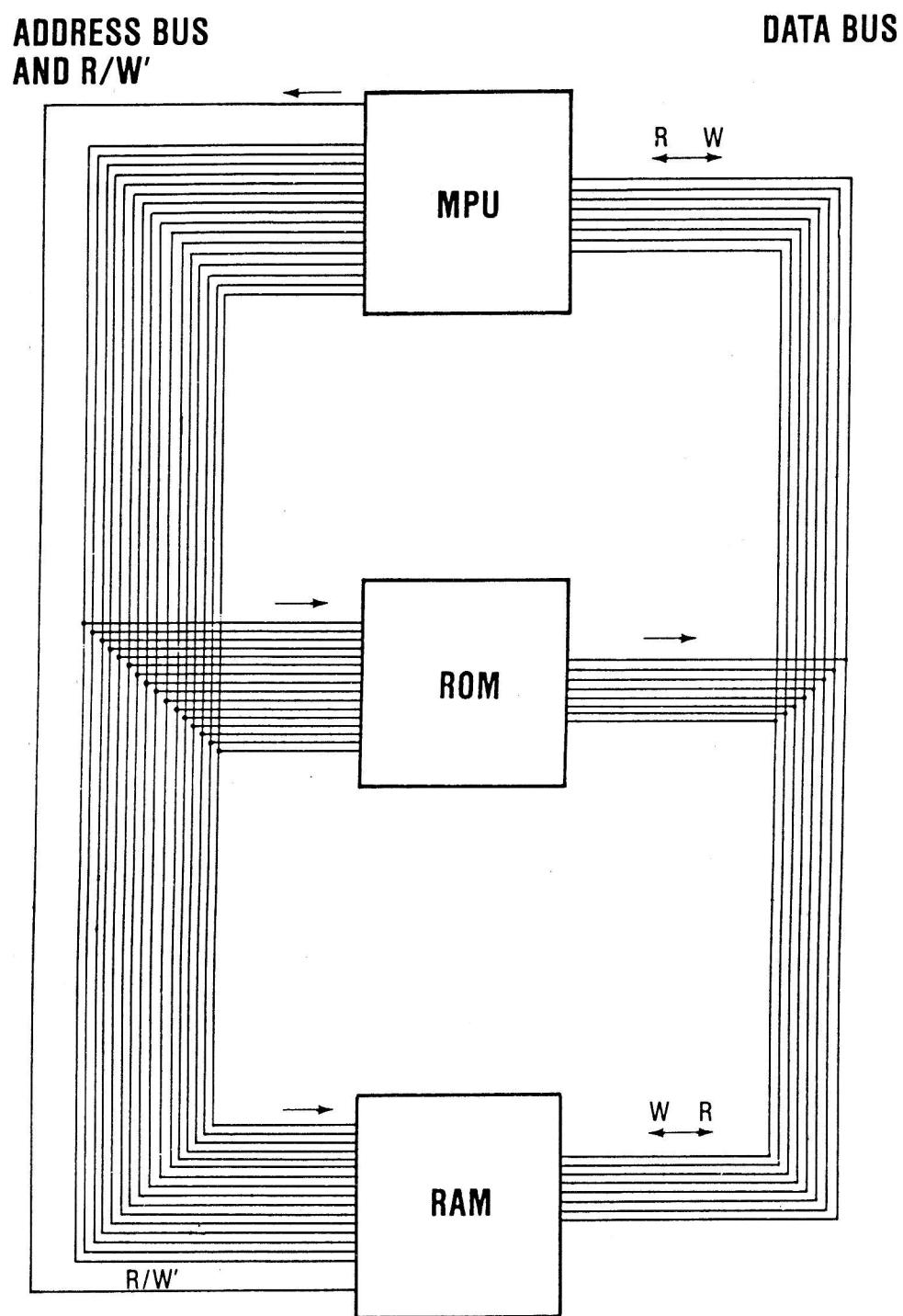

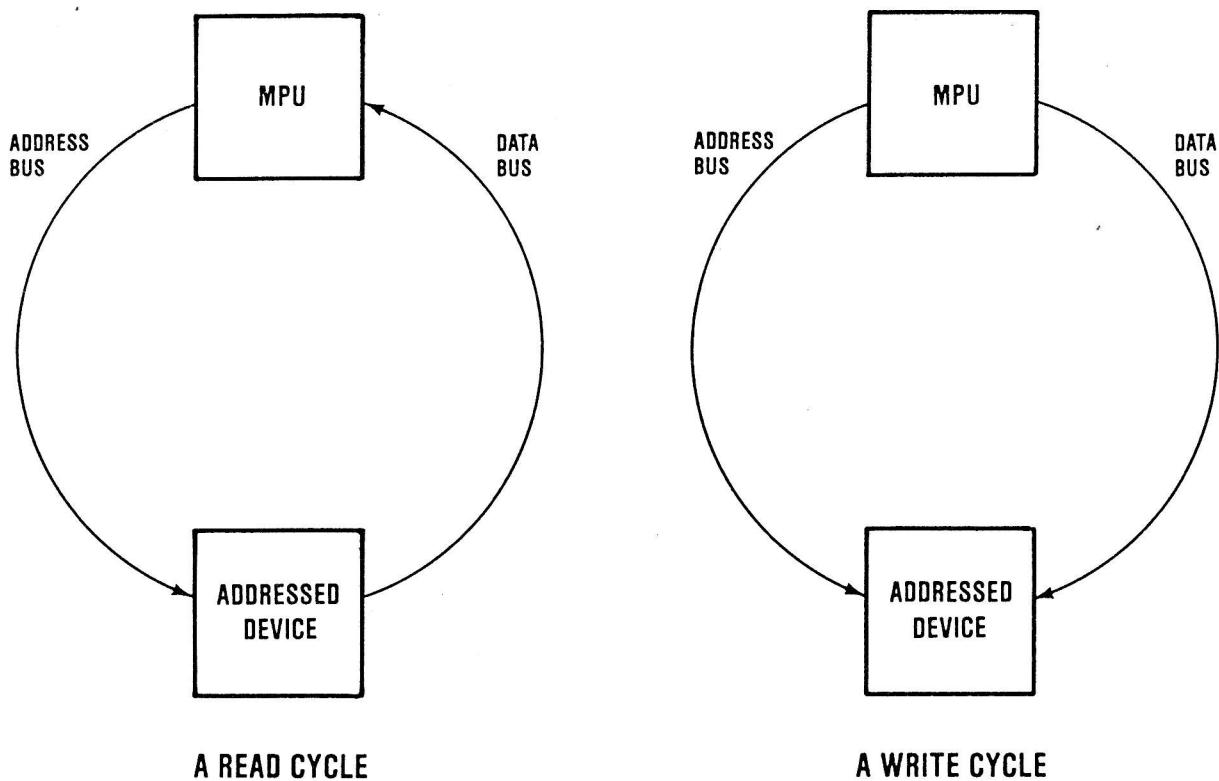

Der Apple //e ist so aufgebaut, daß der 6502 mit einer Vielzahl von anderen Bausteinen kommunizieren, d.h. Daten austauschen kann. Der Prozessor gibt zu diesem Zweck mit einem bestimmten Taktenschlag eine *Adresse* aus. Über diese Adresse wird der jeweilige Baustein angesprochen, mit der der Prozessor Daten austauschen will. Die entsprechenden Leitungen werden als *Adressbus* bezeichnet. Über den Adressbus wird diese Adresse an alle Bausteine des Computers weitergegeben, mit denen der Prozessor Daten austauschen kann. Nach Ausgabe dieser Adresse werden Daten über einen weiteren Satz von Leitungen, dem *Datenbus*, übertragen - entweder von einem durch die Adressausgabe aktvierten Baustein in Richtung Prozessor (Lesen) oder vom Prozessor zu einem Baustein (Schreiben).

Für beide Transferrichtungen werden dieselben Leitungen verwendet, der Datenbus wird deshalb als *bidirektional* bezeichnet. Damit über die Adressausgabe angesprochene Bausteine wissen, ob der Prozessor Daten lesen oder schreiben will, existiert eine weitere Leitung mit der Bezeichnung R(ead)/W(rite) Control, deren Zustand ("0" oder "1") die Richtung des Datentransfers signalisiert. Diese Leitung wird vom Prozessor gesteuert und von allen anderen Bausteinen nur gelesen, d.h. ausgewertet.

Der 6502 hat 16 Adressausgänge, über die der Zustand des Adressbusses gesetzt wird. Der Adressbus wird von allen anderen Bausteinen nur gelesen und hat also nur eine mögliche Richtung, er wird deshalb als *unidirektional* bezeichnet. Jede einzelne dieser Leitungen kann vom Prozessor auf "Spannung" (entspricht "1") oder "keine Spannung" (entspricht "0") gesetzt werden. Der Wert einer Adresse ergibt sich aus den Spannungswerten aller 16 Leitungen zusammen und geht folgenderweise von 0000 0000 0000 0000 (alle Adressleitungen "0") bis 1111 1111 1111 1111 (alle Adressleitungen "1"). In hexadezimaler Darstellung ergeben sich damit Adressen von \$0000 bis \$FFFF, die Umrechnung in Dezimalschreibweise ergibt mögliche Adressnummern von 0 bis 65535.

Der 6502 verfügt über 8 Datenein- und -ausgänge, die je nach der gewünschten Richtung des Datenflusses entweder als Eingänge (Lesen) oder als Ausgänge (Schreiben) funktionieren. In derselben Weise wie bei den Adressleitungen kann jede Datenleitung entweder den Zustand "1" oder "0" annehmen. Die Zustände aller acht Leitungen zusammen ergeben ein Datenwort des Prozessors, die darstellbaren Kombinationen gehen von 0000 0000 bis 1111 1111 (\$00 bis \$FF bzw. 0 bis 255).

Daten- und Adressleitungen können nur einen von beiden Zuständen annehmen: entweder "Spannung" oder "keine Spannung". Diese Definition ist für digitale Computer charakteristisch und wird als "two-state" (zwei Zustände) oder als *binär* bezeichnet. Die gebräuchlichste Schreibweise zur Bezeichnung der beiden Zustände ist "0" oder "low" für "keine Spannung" und "1" oder "high" für "Spannung". Andere Möglichkeiten sind die Bezeichnungen aus/an oder falsch/wahr.

Der Zustand einer einzigen Leitung ("0" oder "1") ist die kleinste darstellbare Informationsmenge eines Computers und heißt Bit. Der 6502 führt jede Operation mit 8 Bit (einem Byte) auf einmal aus und wird deshalb als *8-Bit-Prozessor* bezeichnet.<sup>1</sup>

Durch die Ausgabe einer Adresse wird jeweils ein bestimmter Baustein innerhalb des Computers angesprochen, d.h. jedem Baustein ist eine eigene Elektronik zugeordnet, die auf bestimmte Adresswerte reagiert und den Baustein aktiviert, wenn "seine" Adresse ausgegeben worden ist. Dieser Vorgang bzw. die entsprechende Elektronik wird als

<sup>1</sup> Diese Definition ist nicht mehr ganz korrekt. Der Terminus 8-Bit-Prozessor bezieht sich auf die interne Verarbeitung von jeweils 8 Bit auf einmal. Im allgemeinen stimmen jedoch interne Wortbreite und Anzahl der Datenleitungen überein - allerdings gibt es inzwischen eine Reihe von Prozessoren, bei denen aus Kostengründen der Datenbus kleiner ausgefallen ist (z.B. 8088, 68008).

Adreßdekodierung bezeichnet. Jede Adresse wird innerhalb des Computers nur einmal verwendet und bezeichnet so eindeutig einen bestimmten Baustein.<sup>2</sup> Für Bausteine, die mehr als einen Speicherplatz haben, reagiert die Adreßdekodierung nicht nur auf eine einzelne Adresse, sondern auf einen Adreßbereich.

Der überwiegende Teil der möglichen Adressen innerhalb des Apple //e wird von Speicherbausteinen belegt. Jede dieser Adressen spricht eine *Speicherstelle* an. In diesen Speicherstellen befindet sich das Programm des Mikroprozessors (wie z.B. der Applesoft-Interpreter) oder ein Datum, das vom Prozessor bearbeitet wird. Der Prozessor verbringt rund die Hälfte der gesamten Laufzeit eines Programms damit, Programmspeicherstellen zu lesen. Die Befehle eines Programms sind sequentiell (d.h. hintereinander) in aufsteigender Folge der Adressen angeordnet. Dadurch besteht das Lesen eines oder mehrerer Befehle aus der einfachen Folge "Adreßausgabe, Einlesen eines Datenwortes, Erhöhung der Adresse um 1; Adreßausgabe...". Die restliche Zeit wird für Manipulation, Speicherung und Einlesen von Daten als Reaktion auf vorher gelesene Programmbefehle verwendet. Diese Befehle können auch die Veränderung des Adreßzählers für Programmbefehle zur Folge haben, d.h. ein "Sprung" innerhalb eines Programms besteht schlicht aus einer kontrollierten Veränderung der Adresse, von der aus der nächste Programmbefehl eingelesen wird.

Für die restlichen Adressen des Apple //e ist der Auswahlmechanismus für die Zuordnung "Adresse-Baustein" derselbe - allerdings "hängen" an den entsprechenden Adressen keine Speicherbausteine, sondern z.B. der Lautsprecher des Apple, der anstelle eines Speicherbausteins aktiviert wird und kein Datenwort speichert, sondern jeweils ein "Klick" produziert.

## Speicherbausteine, Datenorganisation und Adreßdekodierung

Abgesehen von einigen Spezialanwendungen muß jeder Computer über zwei Arten von Speicherbausteinen verfügen: Bausteine, von denen nur gelesen werden kann (ROM), und andere, die sowohl Lesen als auch eine Veränderung ihres Inhalts zulassen (RAM).<sup>3</sup> RAM-Bausteine sind notwendig, damit man ein Programm schreiben und speichern kann, sowie für die Speicherung von Daten, die während eines Programmablaufs verändert werden. Mindestens ein ROM-Baustein ist erforderlich, damit der Prozessor nach Einschalten der Stromversorgung ein Programm zur Verfügung hat, das er abarbeiten kann.

Ein Speicherbaustein (ROM oder RAM) enthält eine Vielzahl von einzelnen Speicherzellen. Jeder dieser Bausteine hat eine Anzahl von Pins ("Beinchen"), über die eine vom Prozessor ausgegebene Adresse ins Innere des Bausteins gelangt, sowie weitere Anschlüsse, über die Daten hinein- bzw. hinaustransportiert werden. Einen Speicherbaustein kann man sich als eine (meist sehr große) Anzahl von Schubladen vorstellen; jede Schublade enthält ein Datum. Die Adreßdekodierung innerhalb des Bausteins sorgt dafür, daß nach Erhalt einer bestimmten Adresse jeweils die richtige Schublade geöffnet wird. Je nachdem, ob gelesen oder geschrieben werden soll (für die Leitung Read/Write Control gibt es einen weiteren Anschluß), wird der Inhalt der Schublade über die Datenanschlüsse ausgegeben (der Speicherbaustein bringt die Datenleitungen auf einen dem Schubladeninhalt entsprechenden Pegel) oder die an den Datenanschlüssen anliegenden "Nuller" und "Einser" werden in die Schublade hineingelegt. Nach Ende des Prozesses wird die Schublade wieder zugemacht, ihr Inhalt bleibt solange im Verborgenen, bis dieselbe Adresse erneut angesprochen wird.

Der Unterschied zwischen RAM und ROM liegt darin, daß RAM-Daten verändert werden können, in einem ROM gespeicherte Daten dagegen nicht: die "Schubladeninhalte" eines ROMs sind fest installiert. Dafür vergißt ein ROM seinen Inhalt auch dann nicht, wenn die Stromversorgung abgeschaltet wird; ein RAM behält seine Daten nur unter Spannung, sie gehen beim Ausschalten des Computers verloren.

Für den Prozessor sehen ROM und RAM exakt gleich aus - für das Schreiben eines Datenworts existiert keine Rückmeldung im Sinne von "erfolgreich gespeichert". Der Versuch, etwas in einen ROM hineinzuschreiben, ist völlig ungefährlich - allerdings wird man hinterher feststellen, daß die "beschriebene" ROM-Speicherzelle stur ihren alten Inhalt beibehalten hat.

2 Im Apple //e können verschiedene Bausteine abwechselnd in ein und denselben Adreßbereich geschaltet werden ("bank switching"). Aber auch hier gilt, daß zur gleichen Zeit immer nur ein Baustein aktivierbar ist - die Zuordnung eines Bausteins zu einer Adresse bzw. einem Adreßbereich ist dadurch nach wie vor zu jedem Zeitpunkt eindeutig.

3 Das Kürzel ROM steht für "Read Only Memory" (= nur-Lesespicher) und stellt eine korrekte Bezeichnung dar; RAM steht für "Random Access Memory" (= Speicher mit wahlfreiem Zugriff) und ist eine der berühmtesten Bezeichnungen der sog. Murphy-Terminologie, d.h. schlicht falsch. Besser wäre es, RAM als "Random Alterable Memory" (= wahlfrei veränderbarer Speicher) zu interpretieren - schließlich kann auf einen ROM auch "wahlfrei", d.h. ab einer beliebigen Stelle zugegriffen werden. Die Abkürzung RAM stammt aus der Zeit der Lochkarten, die noch der Reihe nach (also nicht "wahlfrei") eingelesen werden mußten.

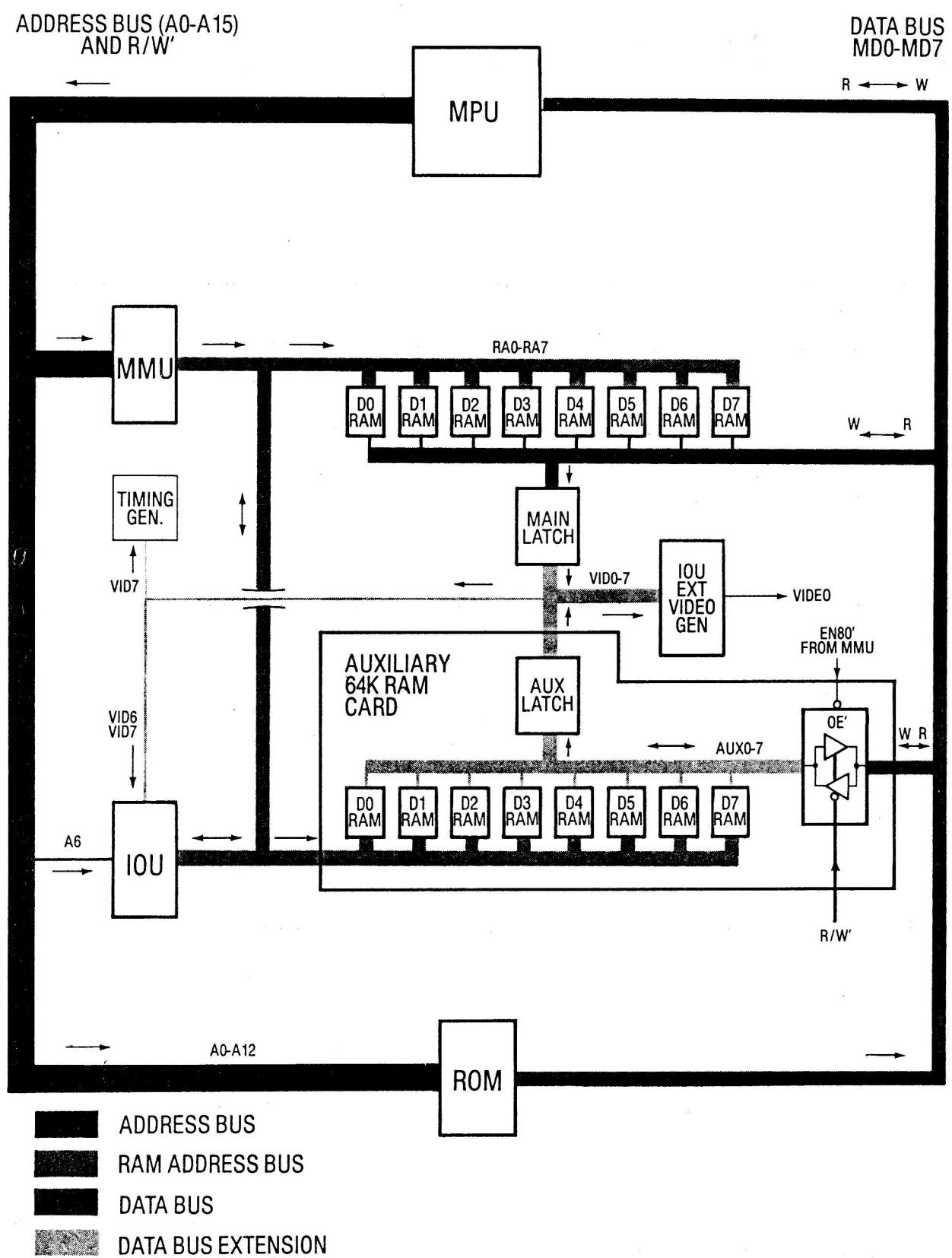

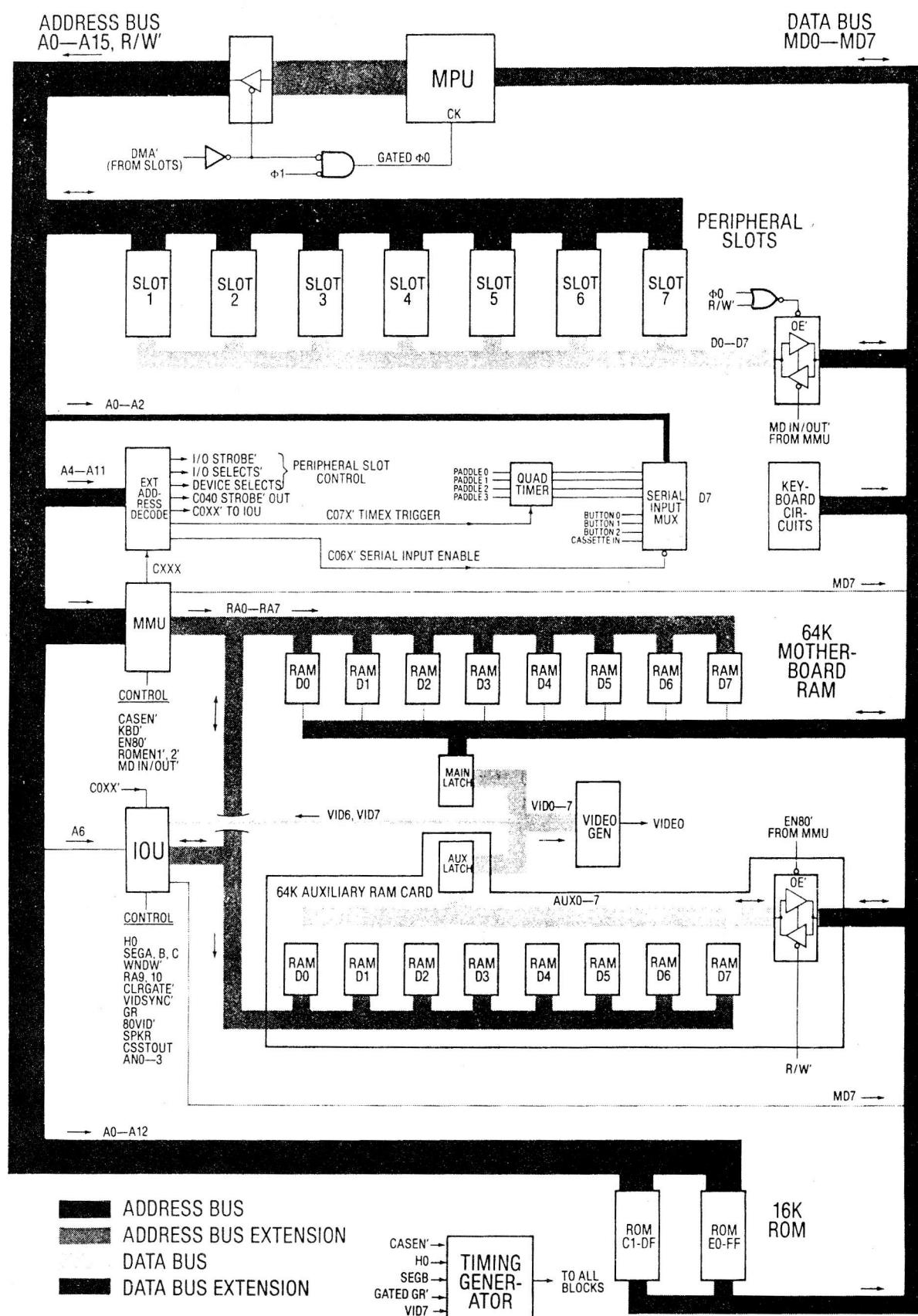

Speicherbausteine können in ihrer internen Organisation verschieden aufgebaut sein. So finden Sie z.B. an der vorderen rechten Ecke der Hauptplatine des Apple //e acht gleichartig aussehende RAM-Bausteine und etwas dahinter 2 breitere ROM-Bausteine. Dieses merkwürdige Verhältnis erklärt sich dadurch, daß jede "Schublade" eines der 8 RAM-Bausteine nur ein einziges Bit aufnehmen kann, eine "Schublade" der ROM-Bausteine dagegen 8 Bit auf einmal.

Da der 6502 immer 8 Bit auf einmal liest bzw. schreibt, ist die Adreßdekodierung des Apple //e so aufgebaut, daß jeder Zugriff auf den RAM des Computers alle acht RAM-Bausteine parallel aktiviert: Jeder RAM-Baustein ist mit allen Adreßleitungen, aber nur mit einer einzigen der acht Datenleitungen verbunden. Ein Zugriff auf den ROM aktiviert (je nach Wert der ausgegebenen Adresse) entweder den einen oder den anderen ROM-Baustein, wobei jeder ROM-Baustein mit allen acht Datenleitungen auf einmal verbunden ist.

Der Apple //e enthält 65536 Byte RAM-Speicherplatz. Diese Menge wird normalerweise als 64 kByte (64 \* 1024 Byte) bezeichnet. Darüber hinaus ist auf der Hauptplatine die entsprechende Elektronik für den Einbau weiterer 64 kByte RAM ("AUX-RAM") in dem speziellen Steckplatz der 80-Zeichen-Karte vorgesehen. Außerdem enthält die Hauptplatine noch 16 kByte ROM-Speicherplatz - damit ergeben sich insgesamt 144 kByte. Die Lösung des Rätsels, wie man für 144 kByte mit insgesamt 65536 Adressen auskommt, liegt wiederum in der Adreßdekodierung: Derselbe Mechanismus, der bei einem Zugriff auf den RAM-Bereich alle acht RAM-Bausteine aktiviert und bei einem Zugriff auf den ROM-Bereich einen der beiden ROM-Bausteine, ist auch für die *Bankumschaltung* innerhalb dieser 144 kByte zuständig. Es sind immer nur 64 kByte auf einmal adressierbar - aber welche Bausteingruppe durch die entsprechenden Adressen angesprochen wird, bestimmt die Adreßdekodierung.

Die 64 kByte RAM auf der Hauptplatine des //e entsprechen einem Apple II mit einer 16 kByte-Erweiterung ("Language Card") in Steckplatz 0. Der durch Adressen im Bereich von \$0000 bis \$BFFF angesprochene RAM-Bereich entspricht dem des Apple II, durch Adressen im Bereich \$D000 bis \$FFFF werden entweder die oberen 16 kByte des RAMs oder der ROM angesprochen. Der Bereich von \$D000 bis \$DFFF existiert dreifach: entweder als "Bank 1" und "Bank 2" der oberen 16 kByte RAM oder als Teilbereich des ROMs. Im Unterschied zum Apple II schaltet ein RESET in diesem Bereich immer auf den ROM um. Wenn über die 80-Zeichen-Karte im speziellen Steckplatz noch weitere 64 kByte RAM angeschlossen sind, verhalten sich die oberen 16 kByte dieses RAMs in derselben Weise wie der RAM auf der Hauptplatine, d.h. ein Zugriff auf den Adreßbereich \$D000 bis \$FFFF selektiert entweder den ROM der Hauptplatine oder den AUX-RAM, wobei der Bereich \$D000 bis \$DFFF hier ebenfalls in "Bank 1" und "Bank 2" unterteilt ist. Ein Apple //e mit erweiterter 80-Zeichen-Karte hat somit das RAM-Äquivalent von zwei kompletten Apple II+, jeweils mit einer 16 kByte-Erweiterung in Steckplatz 0.

Der Apple //e benutzt sogenannte *dynamische* RAM-Bausteine, die periodisch einen *Refresh* ("Auffrischung") benötigen. Das bedeutet, daß jede Speicherzelle ihren Inhalt nach kurzer Zeit "vergißt" - wenn sie nicht jemand in gewissen Zeitabständen daran erinnert. Falls Ihnen das etwas absonderlich vorkommt - diese Art von Bausteinen wird in fast jedem Computer verwendet, in dem größere Mengen an Speicherplatz benötigt werden. Aus technischen Gründen, auf die wir hier nicht weiter eingehen wollen, bringt man in einem dynamisch aufgebauten RAM-Baustein ein Vielfaches an Speicherzellen unter als in seinem Gegenstück, dem statischen RAM. Der Preis dafür ist ein gewisser Mehraufwand an Elektronik, um für einen konstanten Refresh zu sorgen. Die Elektronik auf der Hauptplatine ist jedenfalls nicht nur für den Refresh der normalen 64 kByte, sondern auch für den der zusätzlichen 64 kByte AUX-RAM im speziellen Steckplatz eingerichtet.

In den beiden ROM-Bausteinen auf der Hauptplatine befindet sich die *Firmware* des Computers. Mit dieser Wortschöpfung soll zum Ausdruck gebracht werden, daß es sich dabei um ein Programm (Software) handelt, das aber unveränderlich ist und damit irgendwo zwischen Soft- und Hardware (= Elektronik des Computers) liegt. Die Firmware enthält das *Monitorprogramm* des Apple mit einigen zusätzlichen Routinen für den Betrieb der (optionalen) 80-Zeichen-Karte, den Applesoft-Interpreter sowie einen Selbsttest des Computers. Das Monitorprogramm enthält die Programmteile, die der Prozessor nach Einschalten der Stromversorgung durchläuft (*Boot* bzw. den ersten Teil davon), sowie die generellen Routinen zur Ein- und Ausgabe von Zeichen und das normalerweise als "Monitor" bezeichnete Programm, mit dem man einzelne Speicherstellen des Computers ausgeben und/oder verändern kann. Applesoft BASIC ist der fest eingebaute BASIC-Interpreter des Apple //e; die Routinen für die 80-Zeichen-Karte sind eine Erweiterung der bereits im Monitor vorhandenen Ein- und Ausgaberoutinen für den 40-Zeichen-Modus; das Selbsttestprogramm überprüft die Hauptfunktionen des Computers und die Datensicherheit des RAMs.

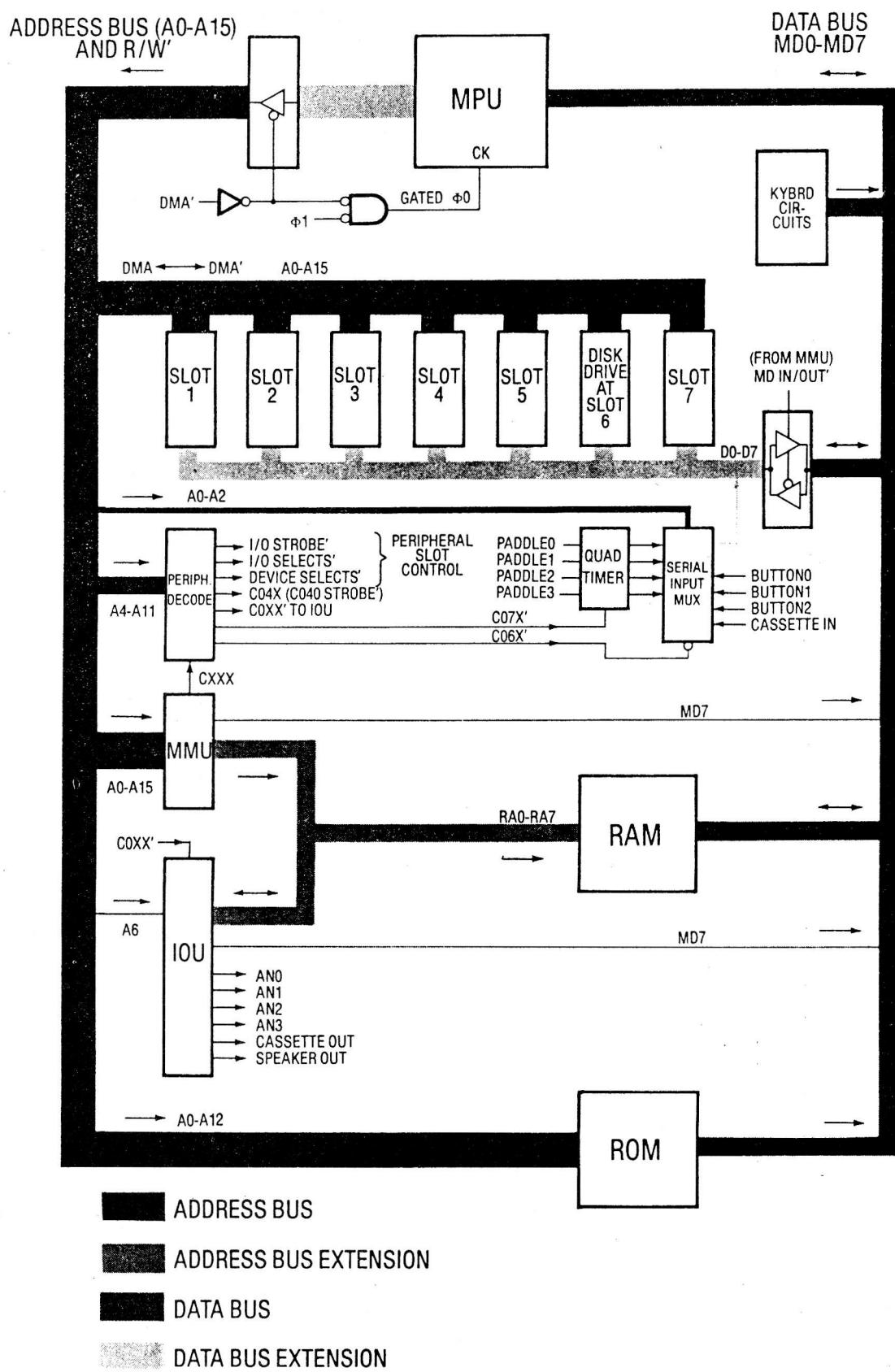

## Die Steckplätze für Zusatzkarten

Die Steckplätze des Apple sind wohl einer der Hauptgründe für die Popularität der Apple II-Serie. Der //e besitzt nur noch sieben davon, der beim Apple II für die Speichererweiterung vorgesehene Steckplatz 0 ist entfallen - schließlich hat der //e bereits standardmäßig 64 kByte RAM. Alle sieben Steckplätze haben eine Verbindung zum Adreß- und Datenbus des Computers sowie zu den wichtigen Kontrollsignalen RESET', READY, NMI', IRQ' und DMA'.<sup>4</sup> Diese Signale finden Sie im Detail in Kapitel 4 besprochen. Wichtig ist hier nur, daß eine entsprechende Zusatzkarte über die Kontrolle dieser Signale den Apple mehr oder weniger auf den Kopf stellen kann: der 6502 kann von einer Zusatzkarte aus unterbrochen, angehalten und sogar völlig von der restlichen Elektronik des Computers getrennt werden. Damit ist es möglich, in einen der Steckplätze einen völlig anderen Prozessor zu installieren, dem sämtliche Funktionen des Apple zur Verfügung stehen. Eine CP/M-Karte mit einem Z80-Prozessor darauf ist zwar das populärste, aber bei weitem nicht das einzige Beispiel dafür. In die umgekehrte Richtung funktioniert das genauso: eine Zusatzkarte kann so konstruiert werden, daß sie auf entsprechende Signale des 6502 reagiert. Die Controller-Karte für die Diskettenlaufwerke beispielsweise reagiert auf RESET' und schaltet daraufhin den Motor der angeschlossenen Diskettenlaufwerke aus.

Jeder Steckplatz ist einem bestimmten Adreßbereich zugeordnet und kann vom Prozessor auf dieselbe Weise wie der RAM angesprochen werden. Für den Apple II und den //e existieren auf dem europäischen Markt mehr als 50 populäre Zusatzkarten sowie eine nicht abschätzbare Zahl von "Exoten".

Mit den Steckplätzen sind noch weitere Signale und Leitungen verbunden, die hier nicht im einzelnen aufgeführt werden. Sie betreffen das "Timing", also die Zeitkontrolle der Elektronik, die Stromversorgung und Auswahlsignale der Adreßdekodierung. Zusammengenommen ermöglichen alle Verbindungen die komplette Integration einer Zusatzkarte in die Elektronik des Apple //e.

## Der spezielle Steckplatz

Im Gegensatz zu seinen Vorfahren verfügt der Apple //e über einen weiteren Steckplatz mit 60 (anstelle von 50) Kontakten, der auch durch seine Lage auf der Hauptplatine von den anderen Steckplätzen abgesetzt ist. Diesem Steckplatz fehlen einige Signale wie z.B. I/O SELECT' und eine vollständige Verknüpfung mit Daten- und Adreßbus.

Er ist für Zusatzkarten vorbereitet, die zusammen mit der Videoelektronik arbeiten bzw. ihre Funktionen erweitern, indem sie das Zeitverhalten der Bilderzeugung ändern. Genutzt wird dieser Steckplatz in den allermeisten Fällen von der speziellen 80-Zeichen-Karte des //e, die nicht nur 80 Zeichen, sondern auch doppelt hoch auflösende Grafik zur Verfügung stellt und in der Form als "erweiterte 80-Zeichen-Karte" weitere 64 kByte RAM ("AUX-RAM") enthält.

Damit verfügt der Prozessor des Apple insgesamt über 128 kByte RAM, die natürlich auch wieder über die Adreßdekodierung so selektiert werden, daß immer nur 64 kByte zur gleichen Zeit erreichbar sind. Funktionen, die sich auf die Generierung von Videosignalen beziehen, wie z.B. ein PAL-Modulator oder ein RGB-Ausgang, können durch "normale" Karten in einem der Steckplätze 1 bis 7 erreicht werden - bei der Konstruktion einer Karte, die die horizontale Auflösung der Bildschirmelektronik verdoppelt, dürften allerdings erhebliche Anstrengungen und Umwege notwendig sein.

Trotz des Fehlens verschiedener "typischer" Signale für normale Zusatzkarten scheint die Anwendung des speziellen Steckplatzes allerdings nicht auf 80-Zeichen-Karten mit und ohne Speichererweiterung beschränkt zu sein - momentan sind bereits Karten für diesen Steckplatz auf dem Markt, die außer einer 80-Zeichen-Darstellung auch noch einen Z80-Prozessor enthalten.

<sup>4</sup> Das Apostroph (') nach dem Namen eines Signals zeigt an, daß die entsprechende Leitung *active low* ist: RESET' bedeutet, daß die RESET-Leitung *inaktiv* ist, wenn sie den Zustand "1" hat (Normalbetrieb), und *aktiv*, wenn sie den Zustand "0" hat. Wir folgen damit den im *Technical Reference Manual* für den Apple //e benutzten Konventionen.

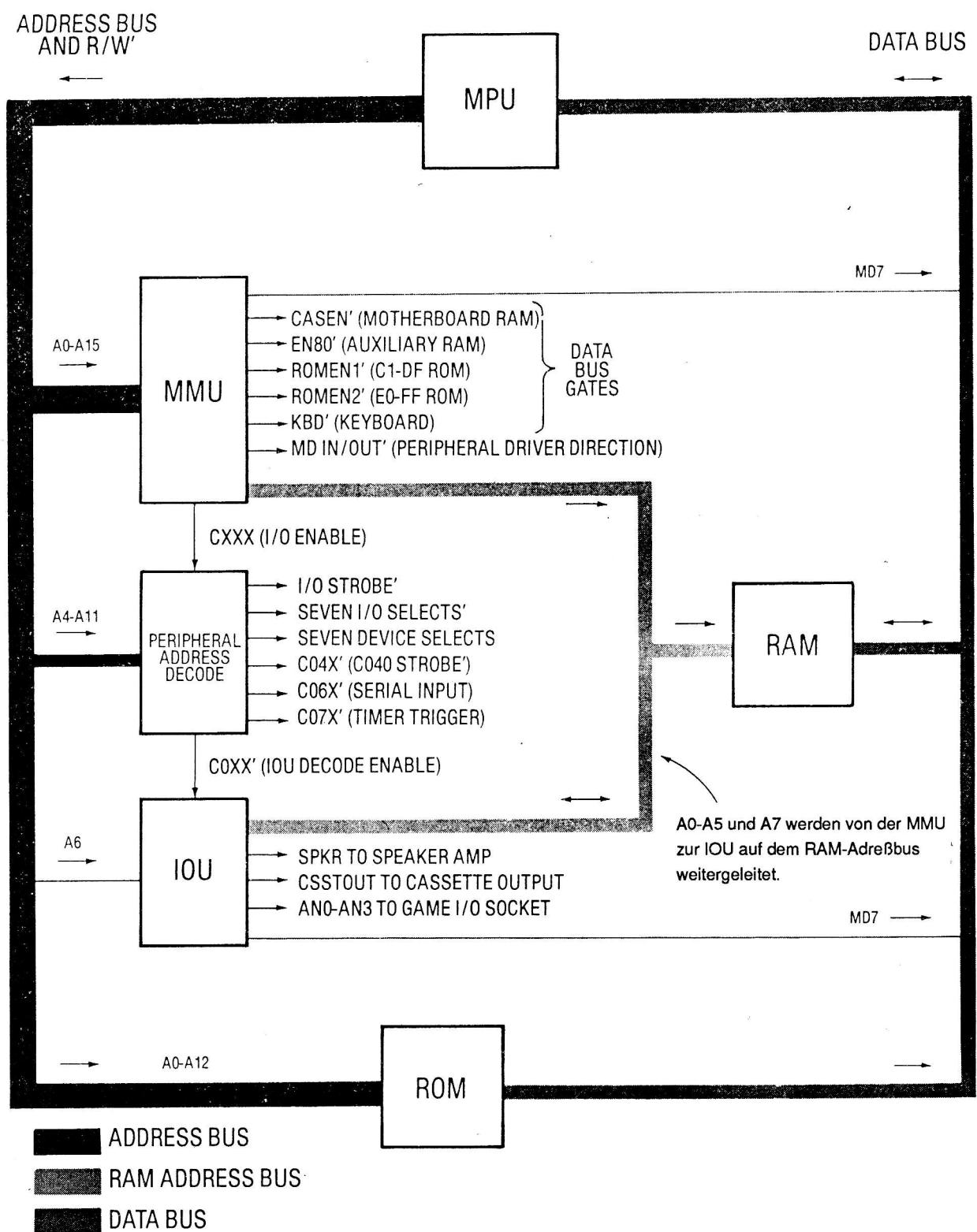

## MMU, IOU und HAL

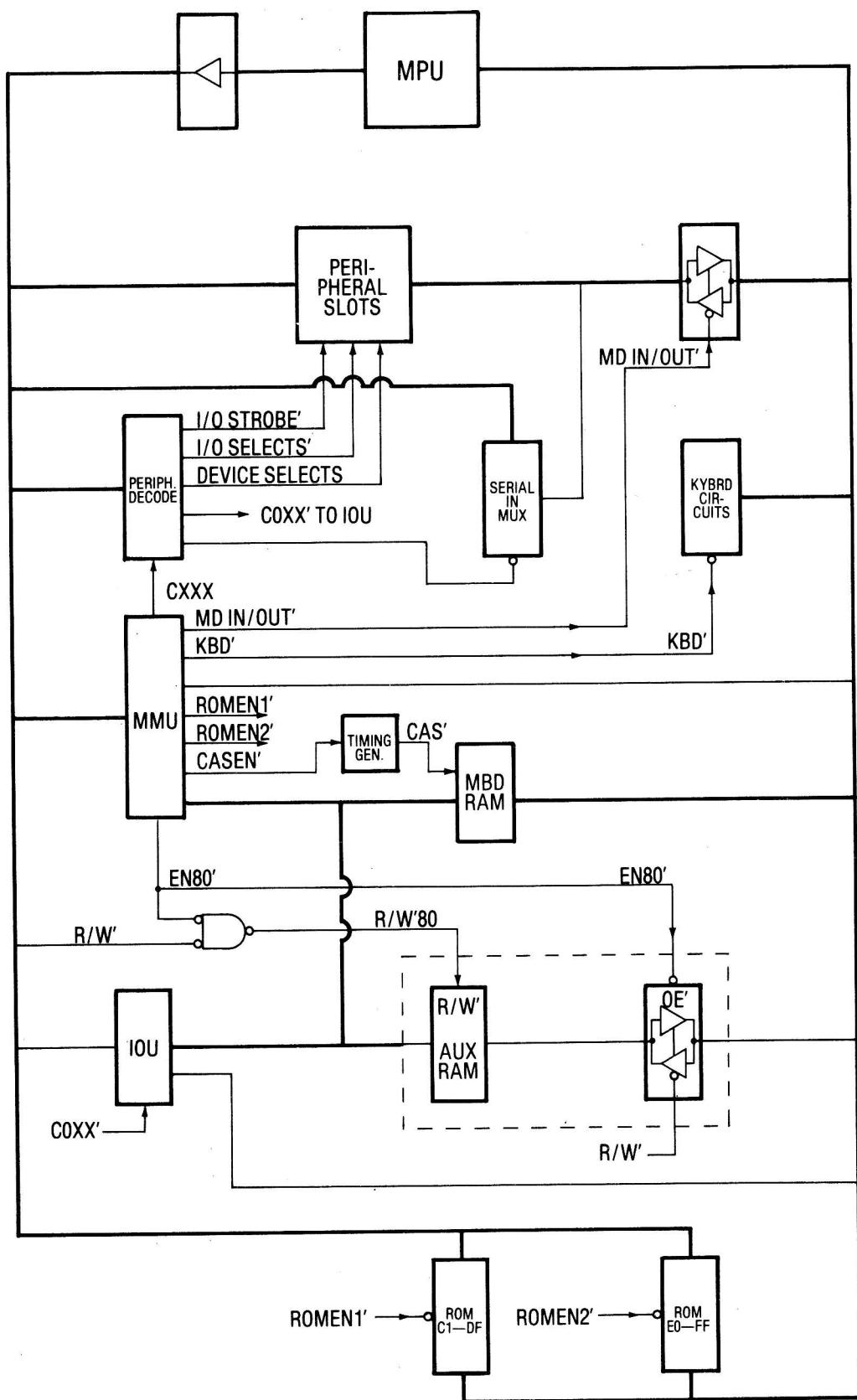

Außer den bereits beschriebenen Funktionsblöcken CPU, RAM, ROM und der (noch nicht erwähnten) Eingabe/Ausgabe benötigt ein Mikrocomputer im Normalfall eine große Zahl kleinerer und einfacherer Chips, die für die reibungslose Zusammenarbeit der einzelnen Funktionsblöcke sorgen. (ATARI hat die entsprechenden Funktionen in der neuen ST-Serie sinnigerweise als "Glue" (= Klebstoff) bezeichnet). Im Apple //e wird der größte Teil dieser Funktionen von drei speziell für Apple, Inc. hergestellten Chips ("Custom-ICs") übernommen. Die Bezeichnungen dieser Bausteine lauten MMU ("Memory Management Unit" = Speicherverwaltungseinheit), IOU ("Input/Output Unit" = Ein-/Ausgabeeinheit) und HAL ("Hard Array Logic" = festverdrahtete Logik).

Die *MMU* enthält eine Reihe von Schaltern, die von einem Programm aus betätigt werden können und deshalb die Bezeichnung *Softswitches* (= Software-Schalter) tragen. Im Gegensatz zu einem physikalischen Schalter ("Hardswitch"?) besteht ein Softswitch aus elektronischen Bauteilen, die einer bestimmten Adresse zugeordnet sind und ebenfalls über Adressdekodierung aktiviert werden. Das Ansprechen einer Adresse, an der ein Softswitch "hängt", bewirkt das Setzen eines bestimmten Zustands. Die meisten dieser Schalter sind mit mehreren Adressen verbunden: das Ansprechen einer Adresse setzt den Schalter "an", das Ansprechen einer zweiten Adresse setzt den Schalter "aus". Softswitches sind ein wichtiger Bestandteil des Apple-Konzepts.

Wie Sie vielleicht bereits erraten haben, kümmert sich die MMU hauptsächlich um die Adressdekodierung und die Verwaltung des Speichers: die verschiedenen Konfigurationen (d.h. welcher Baustein auf einen bestimmten Adressbereich reagiert) werden durch den Stand MMU-interner Softswitches gesetzt. Ein Beispiel dazu: Der Adressbereich \$D000...\$FFFF kann entweder auf "RAM" oder "ROM" geschaltet werden, der dazugehörige Softswitch hat die Adressen \$C080 ("ROM an, RAM aus") und \$C081 ("RAM an, ROM aus"). Je nach Stand dieses Schalters aktiviert die MMU entweder den ROM oder den RAM, wenn eine Adresse im Bereich \$D000...\$FFFF vom Prozessor angesprochen wird.

Um diese Funktionen zu erfüllen, ist die MMU mit allen Adressleitungen verbunden und sieht dem Prozessor quasi bei der Arbeit zu. Außerdem ist die MMU noch mit der Leitung R/W' Control verbunden und kann so im Zusammenhang mit einer gegebenen Adresse bestimmen, ob Daten zu einem Baustein gesendet oder von ihm gelesen werden sollen. Dadurch ist es z.B. möglich, daß der Prozessor Daten von einer Baugruppe liest und sie zu einer anderen Baugruppe schreibt, wobei Quelle und Ziel dieselbe Adresse haben. So verrückt das dazugehörige Programm auch aussieht - der Transfer größerer Datenmengen zwischen dem AUX-RAM und dem RAM der Hauptplatine ist nur so möglich, nämlich durch Setzen der Konfiguration "Lesen von AUX, Schreiben zum Haupt-RAM" oder umgekehrt.

Weitere Funktionen der MMU liegen in der Auswahl und Aktivierung von Zusatzkarten sowie in der Umwandlung von 16-Bit-Adressen in das von den dynamischen RAMs benötigte 8-Bit-Format. Wir werden uns in den Kapiteln 2 und 5 mit weiteren Details in dieser Richtung beschäftigen.

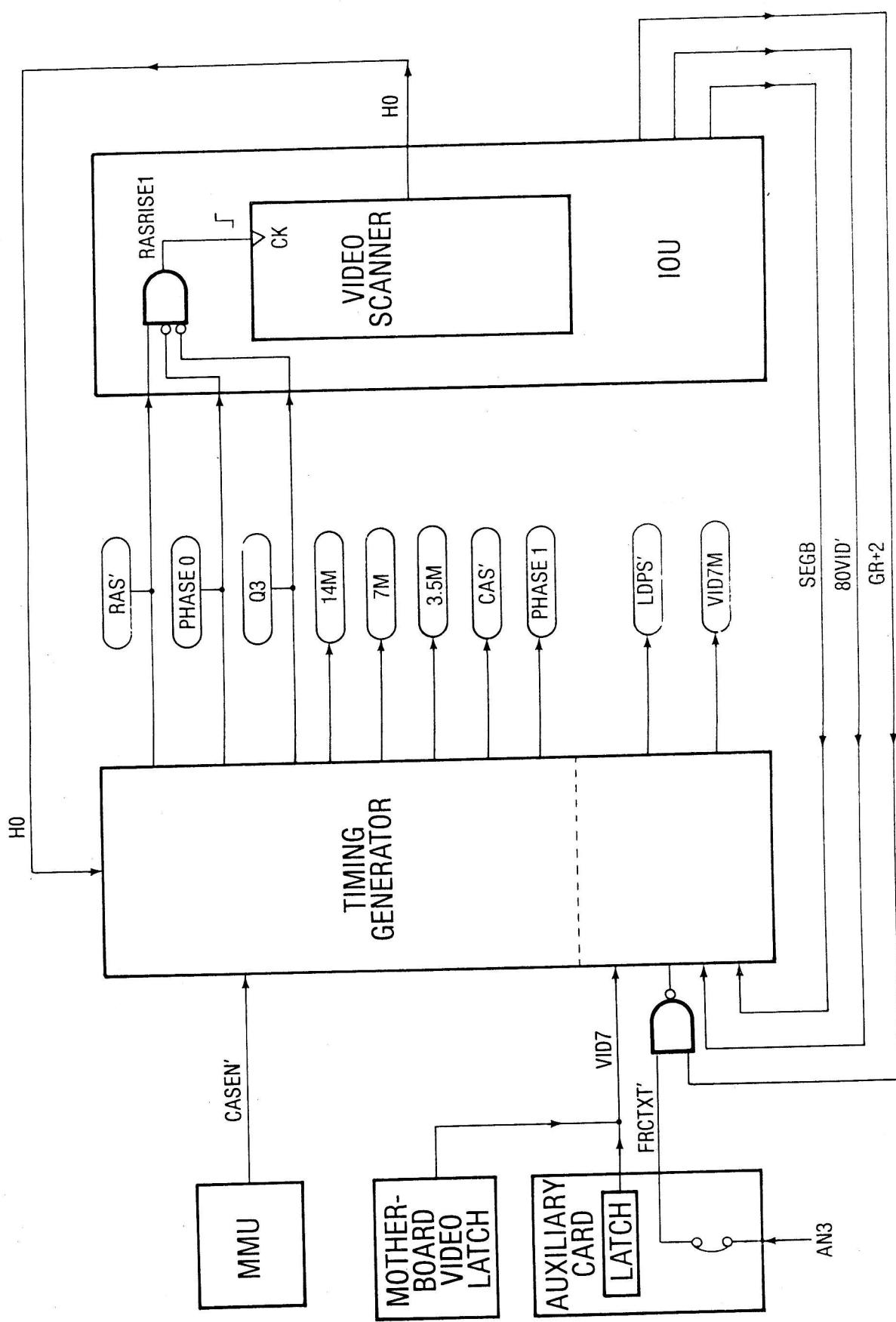

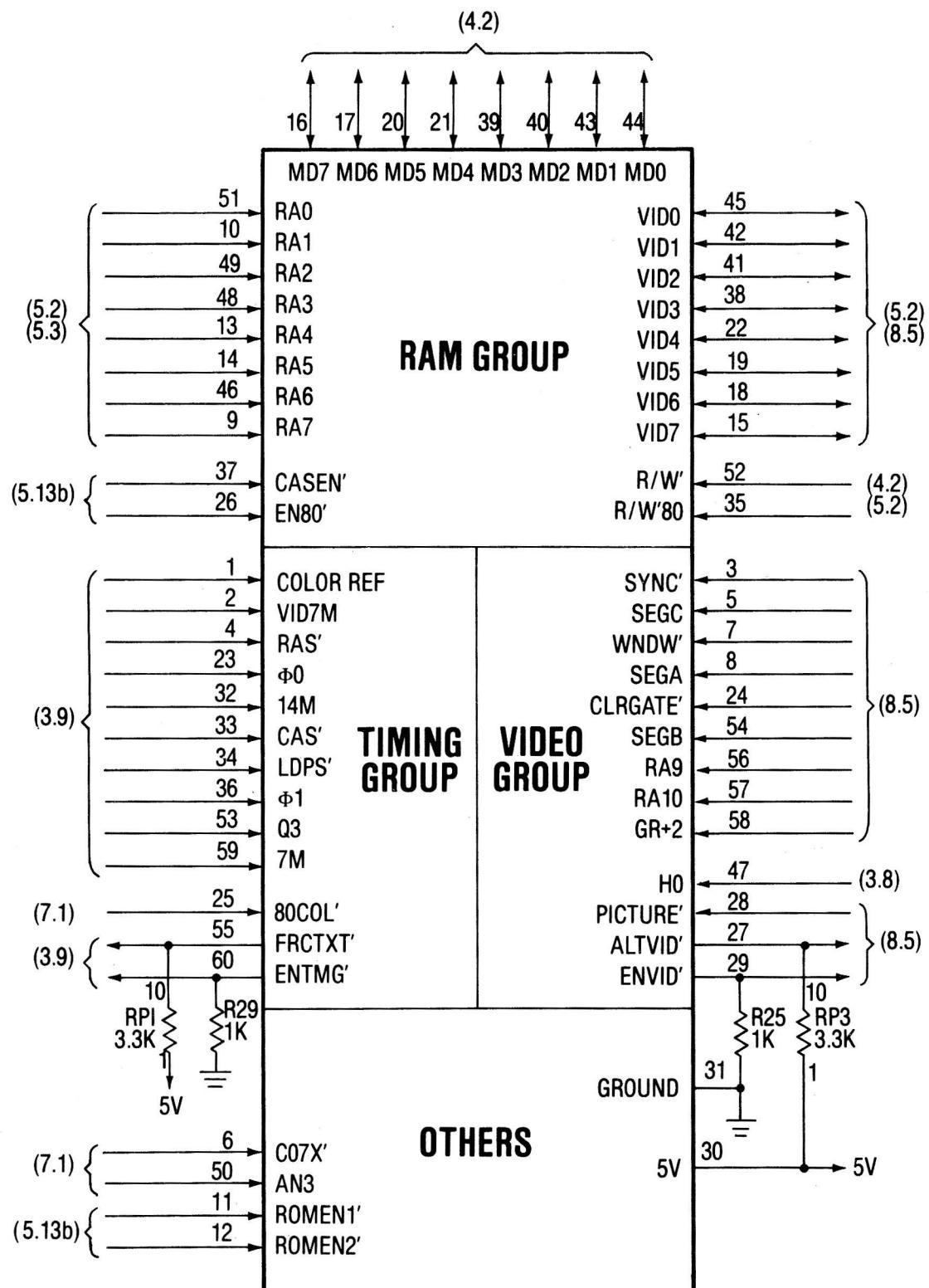

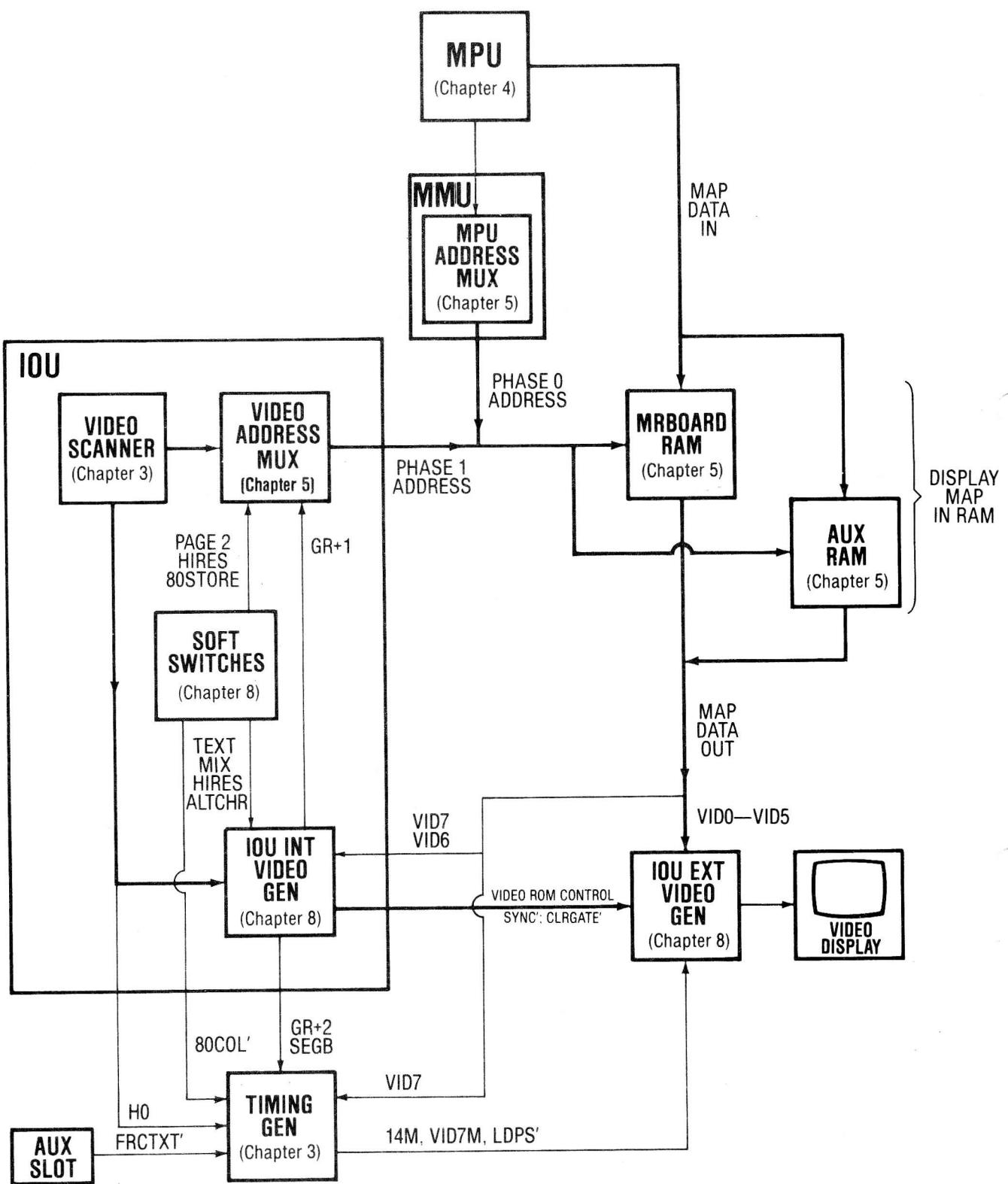

Die *IOU* ist primär für die Erzeugung der Videosignale zuständig. Dafür werden die folgenden Funktionsgruppen benötigt:

- Softswitches zum Setzen der Bildschirmmodi (TEXT, Lo-/HiRes etc.);

- ein Videoscanner, der den entsprechenden RAM-Bereich zyklisch adressiert;

- Elektronik zur Umsetzung einer Videoscanner-Adresse in das von den RAM-Bausteinen benötigte 8-Bit-Format.

Die Elektronik, die die vom RAM ausgegebenen Daten zu dem Signal VIDEO weiterverarbeitet, ist nicht in der IOU enthalten.

Beim zyklischen Durchlauf eines Speicherbereichs dürfen sich der Prozessor und die Videoscanner nicht gegenseitig in die Quere kommen, d.h. es darf immer nur einer der beiden auf den RAM zugreifen. Die IOU benutzt deshalb die Momente, in denen der Prozessor mit internen Vorgängen beschäftigt ist und nicht auf den Speicher zugreift. Dazu ist eine entsprechende Synchronisation notwendig, die hauptsächlich über die Takterzeugung und den HAL gesteuert wird.

Außerdem übernimmt die IOU die Bedienung der gesamten restlichen Ein- und Ausgabemöglichkeiten des Computers wie Tastatur, Kassettenrecorder-Schnittstelle, der "Announciators" und des Lautsprechers.

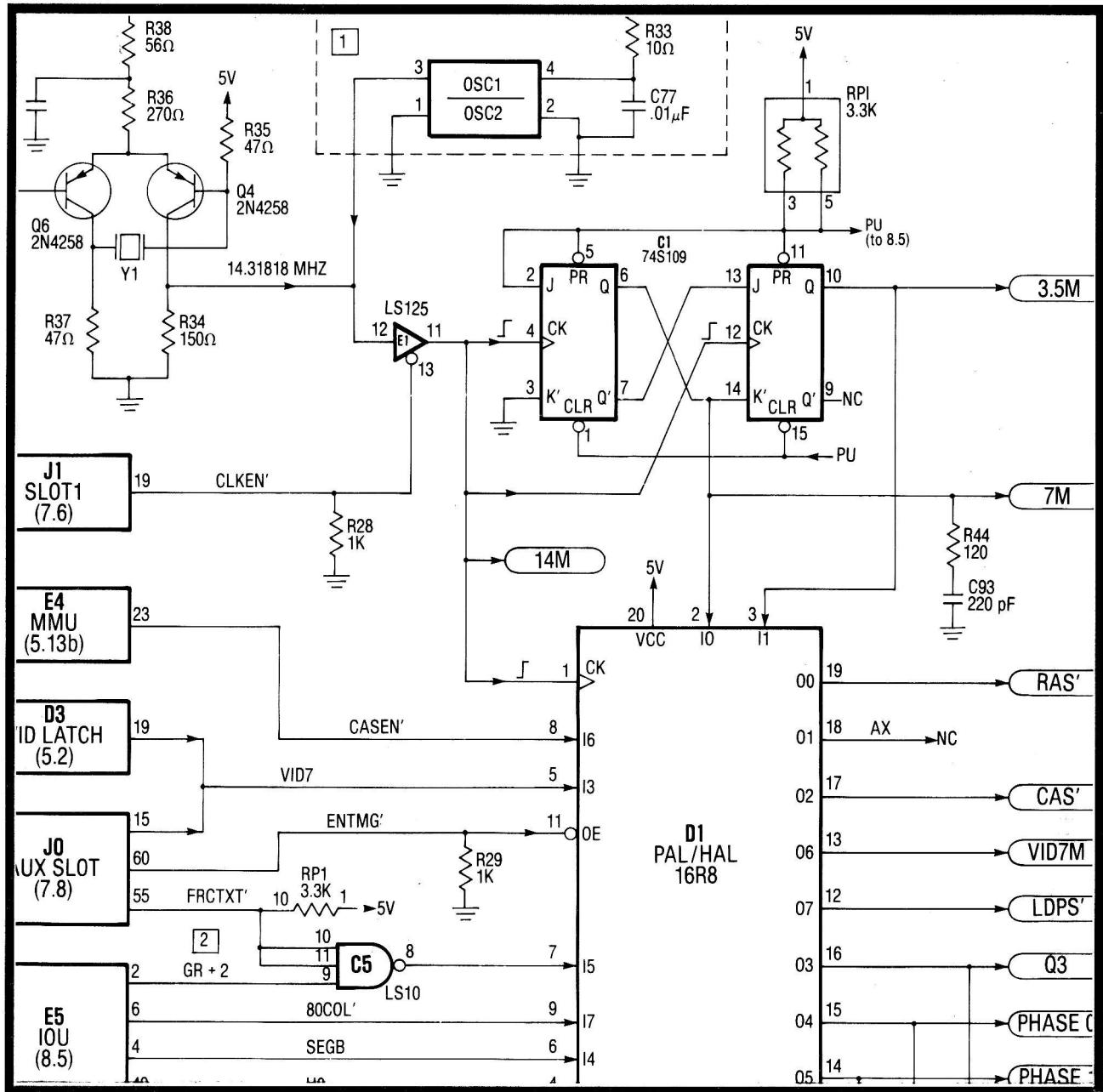

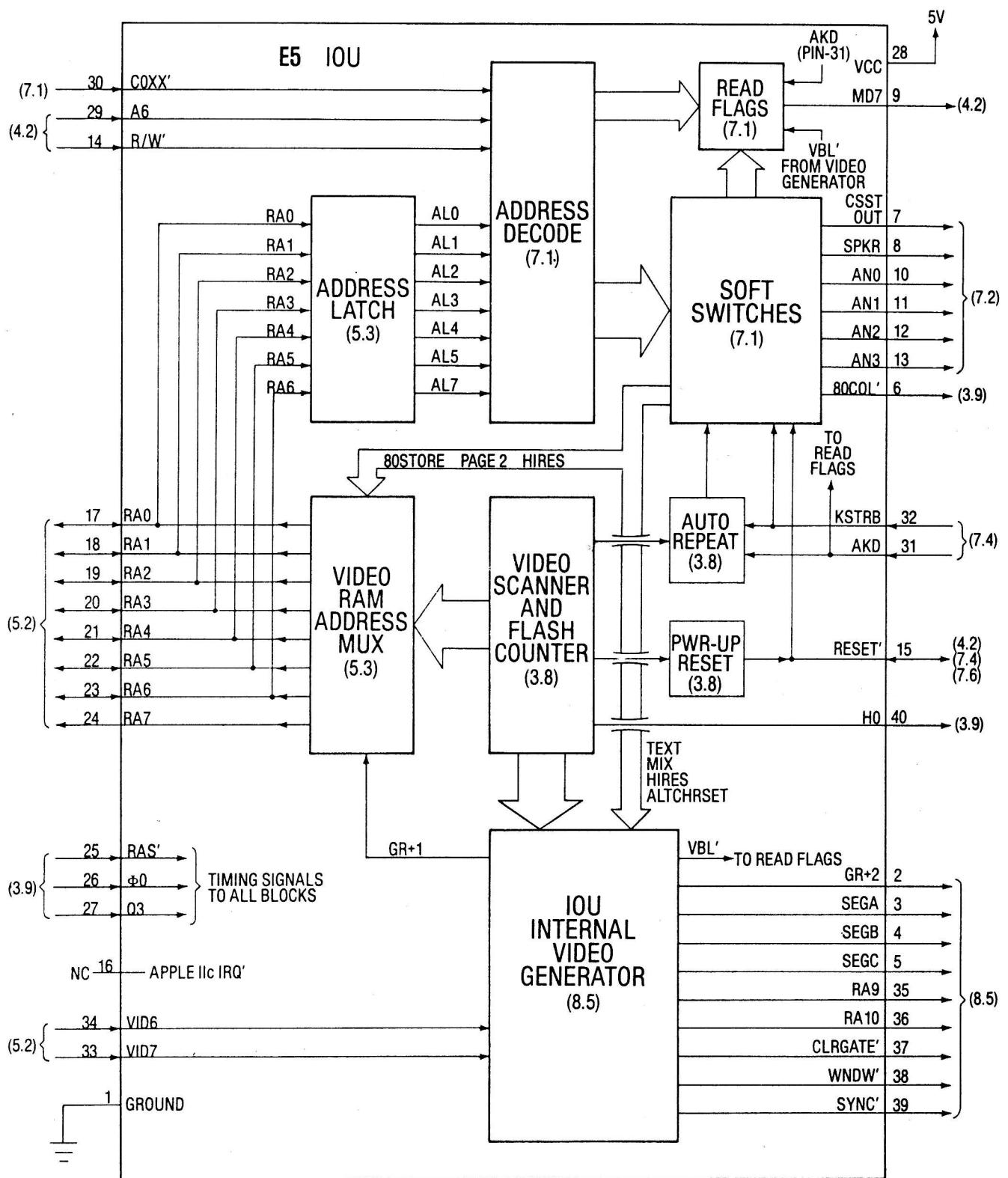

### Bild 1.1 Die Funktionsblöcke der IOU und ihre Anschlußbelegung

Speziell die Schnittstelle zur Tastatur lässt sich noch in einige weitere Unterfunktionen gliedern:

- die "Autorepeat"-Funktion;

- das Signal "Any Key down" (= irgend eine Taste gedrückt);

- der Transfer des Codes einer gedrückten Taste auf den Datenbus des Computers, wenn die Tastaturschnittstelle angesprochen wird.

Einzelne Funktionen der IOU tauchen in fast sämtlichen Kapiteln dieses Buchs auf - Bild 1.1 gibt einen ungefähren Überblick über die Funktionsblöcke der IOU mit dazugehörigen Querverweisen auf die jeweiligen Abschnitte bzw. Kapitel.

Der dritte und letzte spezielle Schaltkreis auf der Hauptplatine des //e ist der HAL. Er ist für die Koordination der diversen Zeitabläufe innerhalb des Gesamtaufbaus zuständig und enthält eine große Menge "primitiver" Schaltkreise, mit denen die Zustände seiner Eingangsleitungen logisch miteinander verknüpft werden. Aus diesen Verknüpfungen werden Signale ("Ausgangsterme") zusammengesetzt, mit denen Zeittakte erzeugt und andere Baugruppen aktiviert werden. Er übernimmt z.B. einen Teil der notwendigen Synchronisation zwischen Videoscanner und Prozessor, indem er für beide Bausteine entsprechend versetzte Taktimpulse erzeugt. (Für Spezialisten: Die Abkürzung HAL steht für "maskenprogrammierter PAL-Baustein"). Details über diese Signale und ihren Zweck finden sie in Kapitel 3.

## Die Videoausgabe

Die *Standardausgabe* beim Apple //e ist der Bildschirm - die Ausgabe über andere Geräte wie z.B. Kassettenrecorder oder Lautsprecher muß erst gesondert aktiviert werden, die Ausgabe eines Videosignals findet sofort nach dem Einschalten des Computers statt. Um es genau zu nehmen: man kann sie überhaupt nicht abschalten, denn sie ist sehr eng mit dem Refresh der RAMs verbunden. Die Videoelektronik erzeugt ein (Farb-)Signal, dessen Zusammensetzung der Fernsehnorm des jeweiligen Landes angepaßt ist, in dem der Computer verkauft wird.

Das vom Apple ausgegebene Videosignal kann direkt in einen farbigen oder monochromen Monitor oder in ein Fernsehgerät mit Videoeingang gespeist werden - über den Antenneneingang eines Fernsehers funktioniert das allerdings nicht, dafür wird ein dazwischengeschalteter HF-Modulator benötigt. Ein HF-Modulator erzeugt ein HF-Signal und moduliert dieses Signal mit dem Videosignal, um so dieselbe Signalart zu erzeugen wie ein Fernsehsender. Innerhalb des Fernsehers wird das HF-Signal de-moduliert, d.h. aus dem modulierten HF-Signal werden die Informationen des Videosignals wieder herausgeholt. Durch diesen doppelten Umwandlungsprozeß, zusammen mit der sowieso schlechteren Auflösung und dem stärkeren Flimmern eines Fernsehers gegenüber einem Computermonitor, haben HF-Modulatoren auch noch einen weiteren Namen bekommen, nämlich "Kopfschmerzen".

Der Apple //e verfügt über drei grundsätzlich unterscheidbare Modi der Bildausgabe: **TEXT**, **LoRes** ("Low Resolution" = niedrige Auflösung) und **HiRes** ("High Resolution" = hohe Auflösung). Im Modus TEXT werden Zeichen und Buchstaben dargestellt, im Modus LoRes (farbige) Blocks und in HiRes (farbige) Einzelpunkte. Zusätzlich sind Mischformen von Grafik und Text möglich: sowohl LoRes als auch HiRes können zusammen mit vier Zeilen Text auf den untersten Zeilen des Bildschirms dargestellt werden. Dieser "Mischmodus" wird als **MIXED** bezeichnet und ist für einfache Anwendungen sehr nützlich, wenn man zu einer Grafik noch Anweisungen oder Erklärungen geben will. Für die meisten ernsthaften Anwendungen sind vier Textzeilen zuwenig - die Auflösung im Modus HiRes ist aber ausreichend für die Darstellung gut lesbarer Buchstaben, und es gibt mittlerweile eine Reihe von Programmen auf dem Markt, mit denen Text auf den Grafikbildschirm gezeichnet werden kann.

Alle drei Modi können sowohl mit der vom Apple II gewohnten Auflösung (40 Zeichen TEXT, 40 LoRes-Blocks und 280 HiRes-Punkte pro Zeile) als auch mit doppelter horizontaler Auflösung (80 Zeichen TEXT, 80 LoRes-Blocks und 560 HiRes-Punkte pro Zeile) ausgegeben werden, die Voraussetzung dafür ist allerdings eine 80-Zeichen-Karte im speziellen Steckplatz.

Jeder der drei Grundmodi hat einen oder mehrere zugeordnete Speicherbereiche im RAM, deren Inhalt von der Videoelektronik zyklisch ausgelesen und in entsprechende Videosignale umgewandelt wird. Diese Speicherbereiche sind:

|            |         |                   |               |

|------------|---------|-------------------|---------------|

| TEXT/LoRes | Seite 1 | \$0400 bis \$07FF | (1 kByte RAM) |

| TEXT/LoRes | Seite 2 | \$0800 bis \$0BFF | (1 kByte RAM) |

| HiRes      | Seite 1 | \$2000 bis \$3FFF | (8 kByte RAM) |

| HiRes      | Seite 2 | \$4000 bis \$5FFF | (8 kByte RAM) |

Nehmen wir als Beispiel an, daß sich die Videoausgabe im Modus TEXT, Seite 1 befindet (dieser Zustand ist direkt nach dem Einschalten des Computers gegeben). In diesem Fall wird der Speicherbereich von \$0400 bis \$07FF rund 50 Mal pro Sekunde ausgelesen und in entsprechende Videosignale verwandelt.

Eine wichtige Konsequenz dieser Art des Bildschirmaufbaus ist, daß die Bildschirmbereiche innerhalb des RAM Programmspeicherplatz benötigen und man (speziell bei der HiRes-Grafik) darum "herumprogrammieren" muß - im Gegensatz zu einer Reihe anderer Computer, bei denen der Bildspeicher einen eigenen RAM-Bereich hat, der z.B. über eine Portadresse angesprochen wird.

Für die Unterscheidung zwischen "Seite 1" und "Seite 2" existiert ein eigener Softswitch mit dem Namen PAGE2, dessen Stellung für *alle* Video-Modi gilt. Nach Einschalten der Stromversorgung und nach einem Druck auf RESET ist Seite 1 aktiv, d.h. der Schalter PAGE2 ist zurückgesetzt.

Alle Bildschirmmodi mit einfacher Auflösung benutzen nur den RAM der Hauptplatine. Während jedes Prozessorzyklus wird ein Byte des Bildspeicherbereichs gelesen, für eine Zeile auf dem Monitor sind es insgesamt 40 Byte. Ausgehend von diesen 40 Byte pro Zeile werden wir die dazugehörigen Modi in diesem Buch als **TEXT40**, **LoRes40** und **HiRes40** bezeichnen, wenn eine Unterscheidung zu den Modi der doppelten Auflösung notwendig ist. Aus Gründen, die im nächsten Absatz erklärt werden, bezeichnen wir die Modi der doppelten Auflösung als **TEXT80**, **LoRes80** und **HiRes80**.

Alle Bildmodi mit doppelter Auflösung benutzen zum einen den bereits gezeigten RAM-Bereich auf der Hauptplatine, zum anderen exakt denselben Bereich innerhalb des AUX-RAMs. Während jedes Zyklus des Prozessors wird erst ein Byte des AUX-RAMs, danach ein Byte des Hauptplatinen-RAMs gelesen, beide Bytes haben dabei dieselbe Adresse. Auf diese Weise werden in derselben Zeit 80 anstelle von 40 Byte zu Videosignalen verarbeitet. Wenn man diese 80 Byte pro Zeile von 0 bis 79 durchnumeriert, dann befinden sich alle Bytes mit einer geraden Nummer im AUX-RAM, die Bytes mit einer ungeraden Nummer befinden sich im RAM der Hauptplatine.

Konsequenterweise ist die Benutzung der doppelt hohen Auflösung nur mit einem zusätzlichen Speicher möglich (der in dem speziellen Steckplatz installiert sein muß). Dabei kann man zwei Arten von Zusatzspeichern unterscheiden:

- Die "normale" 80-Zeichen-Karte enthält nur 1 kByte Speicher und ermöglicht damit die Darstellung von 80 Zeichen Text. Wenn man die Kontaktstifte 50 und 55 auf dieser Karte miteinander verbindet, ist der Modus LoRes80 ebenfalls möglich.

- Eine "erweiterte" 80-Zeichen-Karte enthält dagegen 64 kByte RAM, mit denen alle drei Modi in doppelter Auflösung möglich sind.<sup>5</sup>

Das zyklische Absuchen ("scanning") des Bildspeichers wird, wie bereits gesagt, von der IOU übernommen - der Prozessor wäre dafür auch um ein Mehrfaches zu langsam. Die IOU enthält einen Zähler, dessen Stand der Adresse des nächsten "Videobytes" im Bildspeicher entspricht und über den das Synchronisierungssignal für den Videoausgang erzeugt wird. Dieser Zähler durchläuft den durch den Videomodus gesetzten Bildspeicherbereich zyklisch und wird als *Videoscanner* bezeichnet.

Der Videoscanner spricht den Bildspeicherbereich in einer Weise an, die völlig "transparent" für den Prozessor ist, d.h. der Prozessor merkt nichts davon. In der ersten Hälfte jedes Prozessorzyklus liefert der Scanner die Adresse des nächsten "Videobytes" und "füttert" damit die Bilderzeugung - bei doppelter Auflösung werden dabei der RAM der Hauptplatine und der AUX-RAM im selben Zeitraum gelesen. Die gelesenen Daten werden zwischengespeichert und bis zum Ende des Prozessorzyklus unabhängig vom Prozessor in Videosignale verwandelt. Der 6502 führt Speicherzugriffe nur in der zweiten Hälfte jedes Prozessorzyklus aus. Durch diese Aufteilung stören sich die beiden Funktionen nicht gegenseitig.

Vom Standpunkt des Programmierers aus besteht die Erzeugung eines Bildes aus dem Setzen verschiedener Softswitches, mit denen der gewünschte Bildmodus eingestellt wird, sowie aus dem Berechnen der Speicheradressen einzelner "Bildbytes" und ihrer Veränderung.

<sup>5</sup> Auf Hauptplatinen der Revision "A" ist die doppelt hoch auflösende Grafik auch mit einer erweiterten 80-Zeichen-Karte nicht möglich.

Im Modus **TEXT** werden einzelne Zeichen durch ihren ASCII-Wert innerhalb des Bildspeicherbereichs repräsentiert. Zusätzlich zum ASCII-Wert enthält jedes Byte noch eine Information über die Darstellungsart (NORMAL, INVERSE oder FLASH). Jedes Zeichen belegt dabei ein Byte. Der gespeicherte ASCII-Wert jedes Zeichens bildet eine Adresse innerhalb des Zeichen-ROMs, in dem für jedes ASCII-Zeichen eine Punktmatrix mit  $5 * 7$  Punkten gespeichert ist. Für NORMAL und INVERSE existieren dabei getrennte Speicherbereiche innerhalb des Zeichen-ROMs, die zueinander invertierte Punktmatrizen enthalten. Wir werden später noch einmal darauf zurückkommen. Der Apple //e verfügt über 96 darstellbare TEXT-Zeichen, die NORMAL und INVERSE dargestellt werden können. 64 davon können zusätzlich im Modus FLASH dargestellt werden. Beim verbesserten Apple //e enthält der Zeichen-ROM einen //c-kompatiblen Zeichensatz (s. Bild 8.8).

Der TEXT-Bildschirmaufbau besteht im Modus der einfachen Auflösung aus 24 Zeilen mit jeweils 40 Spalten, bei doppelter Auflösung aus 24 Zeilen mit jeweils 80 Spalten.

Die 80-Zeichen-Darstellung auf dem Apple //e ist so ausgeführt, daß sich der Computer wie ein Apple II mit einer eingebauten 80-Zeichen-Karte in Steckplatz 3 verhält. Diese Simulation geht soweit, daß man den //e als "40-Zeichen-Computer" mit einer zusätzlichen Fähigkeit zur Darstellung von 80 Zeichen betrachten kann - der //e schaltet beim Einschalten der Stromversorgung auf den 40-Zeichen-Modus und bleibt in diesem Modus solange, bis explizit die Aktivierung der 80-Zeichen-Karte befohlen wird.

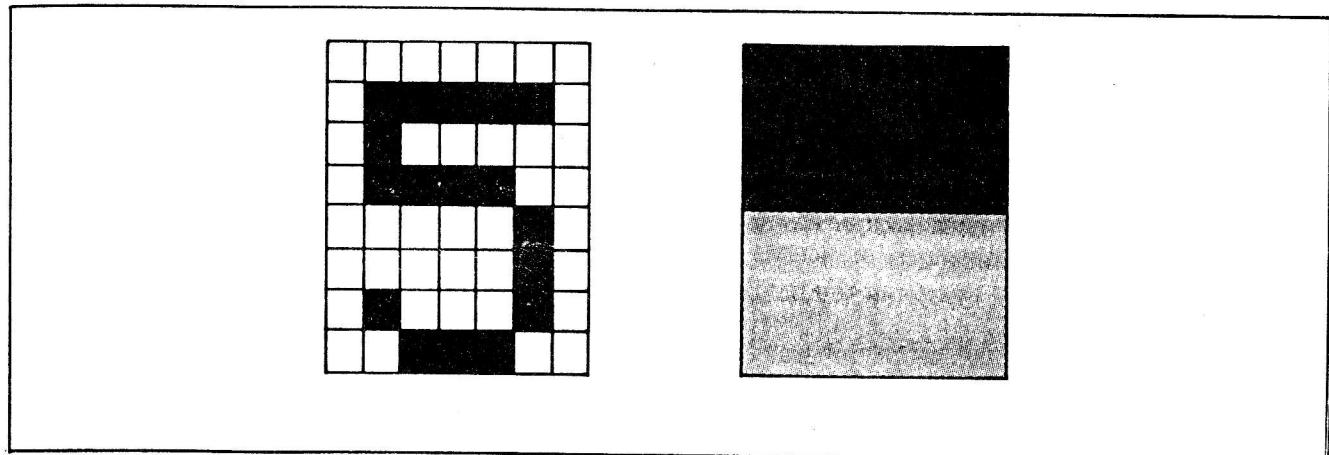

Die **LoRes-Grafik** stellt dem Programmierer einen Bildschirm zur Verfügung, der auf 48 Zeilen entweder 40 (normale Auflösung) oder 80 Spalten pro Zeile enthält (doppelte Auflösung). In jede dieser Spalten kann ein farbiger Block gesetzt werden. Technisch gesehen stehen 16 Farben zur Verfügung - praktisch sind es aber nur 15, weil die beiden Graufarben zwar durch unterschiedliche Muster im Zeichen-ROM erzeugt werden, aber auch auf einem Farbbildschirm exakt gleich aussehen. Wir werden trotzdem bei der Bezeichnung "16 Farben" bleiben.

Die LoRes-Grafik benutzt denselben Speicherbereich wie TEXT - das Arbeitsprinzip des Scanners ist also in beiden Fällen gleich. Die aus den "Bildschirmbytes" erzeugte Adresse im Zeichen-ROM wird um einen "Offset" erhöht, dadurch werden nicht Zeichenmatrizen, sondern Punkt muster adressiert. Um eine von 16 Farben zu kodieren, braucht man 4 Bit, deshalb lassen sich im Speicherplatz für ein ASCII-Zeichen (1 Byte = 8 Bit) zwei LoRes-Blöcke unterbringen und die Auflösung der LoRes-Grafik ist bei gleichem Speicherplatzbedarf doppelt so hoch wie im TEXT-Modus. Es besteht ein direkter Zusammenhang zwischen der Position eines "Buchstabenbytes" und zweier LoRes-Blöcke, der in Bild 1.2 dargestellt ist.

Im Modus **HiRes40** besteht der Bildschirm aus 192 Zeilen mit jeweils 280 Einzelpunkten. Abgesehen von der Farbdarstellung ist der Zusammenhang für den Programmierer erfreulich einfach: Für jedes gesetzte Bit im entsprechenden Speicherbereich wird ein heller, für jedes nicht gesetzte Bit ein dunkler Punkt auf dem Bildschirm erzeugt. Tatsächlich findet hier ebenfalls eine Umsetzung der "Bildschirmbytes" über den Zeichen-ROM statt, die aber den Programmierer nicht zu interessieren braucht. Jedes "Bildschirmbyte" erzeugt 7 Punkte aus D0..D6, das achte Bit wird für die Farberzeugung gebraucht. Jede Bildzeile besteht aus 40 Byte - damit ergeben sich  $7 * 40 = 280$  Bildschirmpunkte pro Zeile. Anstelle einer Punktmatrix, über die jedem Byte des TEXT-Bildschirms eine Matrix mit insgesamt 8 untereinanderliegenden (Video-)Zeilen zugeordnet wird, "bringt" hier jedes Byte nur eine einzige Zeile auf dem Monitor, und wir brauchen deshalb  $8 * 40$  Byte, um den Raum einer TEXT-Zeile auf dem Bildschirm auszufüllen. Die Auflösung in vertikaler Richtung ergibt sich damit zu  $8 * 24 = 192$  Bildpunkten. Soweit zu den einfacheren Dingen.

Das achte Bit jedes Bytes hat eine erheblich kompliziertere Funktion - es bestimmt die *Lage* der restlichen 7 Bits im Bild. Auf einem monochromen Monitor kann man durch Setzen dieses Bits die restlichen 7 Bildpunkte um eine halbe Punktposition verschieben, die theoretische Auflösung der einfachen HiRes-Grafik beträgt damit 560 Bildpunkte pro Zeile. Auf einem Farbbildschirm dagegen bestimmt das achte Bit eine von zwei *Farbgruppen* mit jeweils vier Farben, die ihrerseits durch die bitweise Belegung innerhalb der restlichen sieben Bit jedes Bytes bestimmt werden. Die Farbe eines einzelnen Bildpunkts ist damit sowohl vom Zustand des achten Bits als auch von der "Lage" des Punktes innerhalb des entsprechenden Bytes abhängig. So können z.B. die Farben grün und orange immer nur auf ungeraden, die Farben violet und blau nur auf geraden Horizontalpositionen gezeichnet werden. Die Auflösung für farbige Darstellung sinkt damit auf  $140 * 192$ . Der Versuch, eine grüne Linie (Farbgruppe 0) über einen blauen Hintergrund (Farbgruppe 1) zu zeichnen, ergibt Merkwürdiges: in der Umgebung der Linie färbt sich der Hintergrund orange, weil durch das Zeichnen der grünen Linie die achten Bits gelöscht werden und damit das gesamte Byte von Farbgruppe 1 auf 0 wechselt.

Bild 1.2 TEXT- und LORES-Grafik

HiRes80 stellt einen Bildschirm mit  $560 * 192$  Punkten und beseitigt die vorher angesprochenen Probleme: im Schwarzweiß-Betrieb kann jeder einzelne Bildpunkt unabhängig von den anderen programmiert werden, die Position eines Punktes wird nicht mehr vom achten Bit beeinflußt. Je nachdem, wieviele Farben verwendet werden, geht die erreichbare Auflösung von  $140 * 192$  Punkten mit allen 16 LoRes-Farben (!) in verschiedenen Stufen bis  $560 * 192$  (monochrom).

Diese kurze Beschreibung enthält gerade genug Informationen, um die Komplexität des Themas erkennen zu lassen. In Kapitel 8 werden wir etwas mehr Licht in diese Abgründe bringen. Im Moment sollte die grobe Zusammenfassung ausreichen, daß die erreichbare Auflösung im HiRes-Modus des Apple //e von  $140 * 192$  bis  $560 * 192$  geht und davon abhängt, wieviele Farben benutzt werden und ob HiRes40 oder HiRes80 aktiv ist.

Wie bereits gesagt, wird für HiRes ein erheblich größerer Speicherbereich benötigt als für TEXT und LoRes: in normaler Auflösung werden 8192 Byte auf der Hauptplatine belegt, in doppelter Auflösung kommen noch einmal 8192 Byte innerhalb des AUX-RAMs dazu.

## Die Tastatur

Von einigen speziellen Eingabegeräten wie der Maus und anderen einmal abgesehen, ist die Tastatur die einzige Möglichkeit für den Benutzer, seine Wünsche dem Computer verständlich zu machen. Der Prozessor des Apple verbringt folglicherweise auch den größten Teil seines Lebens in einer recht einfachen Routine mit dem Namen KEYIN (oder GETKEY, falls die 80-Zeichen-Karte aktiviert ist) und tut dabei nichts anderes, als auf einen Tastendruck zu warten. Damit es ihm nicht gar zu langweilig wird, erhöht er für jede Abfrage der Tastatur noch eine Zufallszahl um eins und bringt (auf der 80-Zeichen-Karte) einen Cursor zum Blinken. Pro Betriebsstunde kommen dabei immerhin rund 165 Millionen Tastaturabfragen zusammen, und falls Sie jemand fragt, was ihr Apple denn so tut, können Sie mit ruhigem Gewissen antworten: "Hauptsächlich prüft er, ob eine Taste gedrückt worden ist".

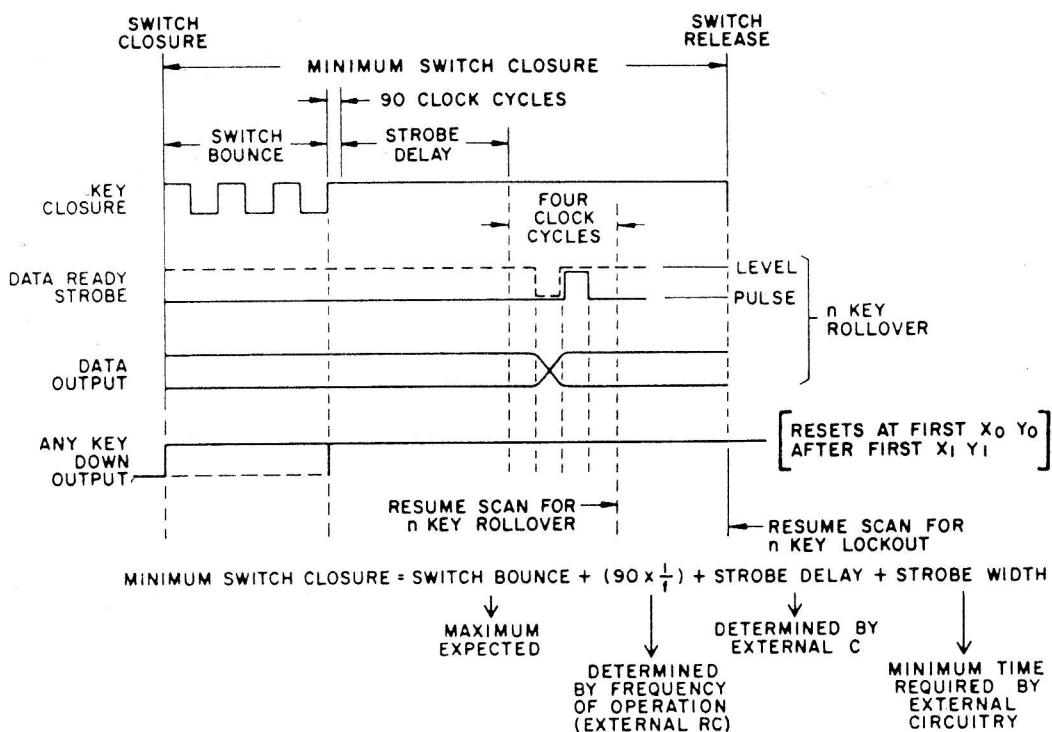

Die Tastatur hat 63 Tasten, welche die Buchstaben des Alphabets, die Zahlen von 0 bis 9, Sonderzeichen und einige Sonderfunktionen repräsentieren. Wenn der //e auf amerikanischen Zeichensatz umgeschaltet ist, entspricht die Tastaturbelegung der von IBM vor Urzeiten hergestellten Schreibmaschine Selectric. Über die IOU ist eine Autorepeat-Funktion realisiert, die den Code einer Taste in schneller Folge wiederholt, wenn diese Taste für längere Zeit gedrückt wird, und es kann von einem Programm aus festgestellt werden, ob irgendeine Taste gedrückt worden ist, ohne das entsprechende Zeichen "abholen" zu müssen. Die Tastatur ist mit einem sogenannten *N-Key Rollover* ausgerüstet, d.h. wenn mehrere Tasten gleichzeitig gedrückt werden, kommt dabei (im Gegensatz zu den früheren Ausgaben des Apple II) kein Unsinn heraus, sondern die Zeichen werden der Reihe nach dem Programm zur Verfügung gestellt. "Gleichzeitiges" Drücken heißt für die IOU immer noch, daß zwischen dem Kontaktschluß einer ersten und einer zweiten Taste ein paar hundert Mikrosekunden vergehen, und das ist ausreichend, um diese beiden Tasten "hintereinander" zu erkennen.

Über die meisten Tasten läßt sich direkt ein dazugehöriges ASCII-Zeichen erzeugen, das durch gleichzeitiges Drücken von SHIFT entsprechend verändert werden kann. Da die Tastatur "echte" ASCII-Zeichen produziert und der Bildschirm ebenfalls ASCII-Zeichen verwendet, ist die Ausgabe eines eingetippten Zeichens eine recht einfache Angelegenheit, die von den eingebauten Routinen der Firmware erledigt wird. (Es gibt immer noch Computer anderer Hersteller, bei denen das nicht der Fall ist, d.h. Tastaturcodes und/oder Bildschirmcodes nicht dem ASCII entsprechen, was vom Programmierer ausgebadet werden muß!)

Die restlichen Tasten haben spezielle Funktionen, als da wären: ESC, DELETE, RESET, TAB, CONTROL, RETURN, SHIFT, CAPS LOCK, offener und geschlossener Apfel und die vier Pfeiltasten.

ESC, DELETE, TAB, RETURN und die Pfeiltasten erzeugen dabei ebenfalls ASCII, allerdings nur durch Übersetzung in einem Programm, wobei ESC und DELETE die einzigen Möglichkeiten sind, die dazugehörigen Codes zu erzeugen. Die Codes der restlichen Tasten lassen sich auch noch auf andere Weise, nämlich durch CONTROL-I, CONTROL-M, CONTROL-U, CONTROL-H, CONTROL-J und CONTROL-K erzeugen. Alle diese Codes erzeugen keine "druckbaren" Zeichen und müssen von einem Eingabeprogramm interpretiert werden, sie werden *Steuerzeichen* genannt.

Die Taste RESET hat keinen ASCII-Wert: Wenn sie zusammen mit der Taste CONTROL gedrückt wird, bringt die IOU die Leitung RESET' auf aktiven Pegel (also "0"). Die Folge davon ist, daß nicht nur der 6502, sondern auch alle Softswitches der MMU und einige Softswitches der IOU zusammen mit allen Zusatzkarten, die auf RESET' reagieren, zurückgesetzt werden.

Die beiden SHIFT-Tasten, CAPS LOCK und CONTROL erzeugen ebenfalls keine ASCII-Zeichen, sie werden direkt von der IOU gelesen und verändern von der IOU ausgegebene Tastaturcodes für eingegebene "normale" Zeichen.

Die Tasten "offener Apfel" und "geschlossener Apfel" sind eigentlich keine Tasten im direkten Sinne und haben keine Verbindung zur IOU - stattdessen entsprechen sie den Tasten 0 und 1 der Spielsteuerungen, die über den GAME I/O (normalerweise zusammen mit einem Joystick) angeschlossen werden können. Sie sind für den Apple //e in das Tastenfeld mit aufgenommen worden, um eine Alternative für "CONTROL-Funktionen" zu bieten: ein Programm kann über das Lesen der Spielsteuerungseingänge bestimmen, ob eine dieser Tasten gedrückt wurde, und daraufhin entsprechend reagieren.

Derselbe Schalter an der Unterseite des Gehäuses, der die Bildschirmausgabe vom amerikanischen Zeichensatz auf einen nationalen Zeichensatz umschaltet, bewirkt auch eine Umschaltung der Tastatur von "amerikanischer" auf "nationale" Belegung.<sup>6</sup> Hinter dieser Umschaltung von einem guten Dutzend Tasten mit einem einzigen Schalter steckt wieder einmal ein ROM: Alle Codes, die durch Tastendrücke erzeugt werden können, sind im *Tastatur-ROM* gespeichert, die Zuordnung "Taste - erzeugter Code" geschieht auch hier wieder über Adressen, deren Wert ("Adreßlage") über diesen Umschalter verändert wird.

Die Tastatur des //e enthält keinen separaten Zehnerblock - allerdings befindet sich neben dem Anschluß der normalen Tastatur auf der Hauptplatine ein weiterer Steckverbinder, über den eine externe Tastatur angeschlossen werden kann. Die Erzeugung der Tastaturcodes für eine externe Tastatur geschieht ebenfalls über den Tastatur-ROMs, so daß durch eine entsprechende Umprogrammierung des ROMs auch auf einem angeschlossenen Zehnerblock beliebige Codes erzeugt werden können.

## Weitere I/O

Die Abkürzung I/O steht für "Input/Output" (= Eingabe/Ausgabe). In diesem Abschnitt wollen wir uns nur auf weitere Funktionen der Hauptplatine beziehen, d.h. uns nicht dem schier unerschöpflichen Thema der Ein-/Ausgabe über Zusatzkarten wie Modems, Druckerschnittstellen, A/D- und D/A-Wandler, Digitizer, Synthesizer etc.,etc. widmen.

Außer den bereits besprochenen Funktionsblöcken "Video" und "Tastatur" enthält der Apple //e auf der Hauptplatine noch einige weitere *serielle* Ein- und Ausgabemöglichkeiten. Eine kurze Erklärung des Begriffs "seriell": Die Eingabe von der Tastatur findet *parallel* statt, d.h. die durch einen Tastendruck erzeugten ASCII-Zeichen werden

<sup>6</sup> Der ab Januar 1986 verfügbare, verbesserte Apple //e hat eine leicht geänderte Tastaturbelegung und schaltet nur noch 6 Zeichen um - so bleibt z.B. bei der deutschen Version auch im amerikanischen Zeichensatz das "Z" neben dem "T".

"auf einmal" eingelesen. Ein ASCII-Zeichen wird durch 7 Bit dargestellt, folglicherweise braucht man dazu (mindestens) 7 Leitungen, auf denen genauso wie auf dem Datenbus jeweils ein Pegel liegt, der ein einzelnes Bit repräsentiert. Im Gegensatz dazu benötigt man für ein serielles Signal (theoretisch!) nur eine einzige Leitung, mit der einzelne Bits *nacheinander* übertragen werden. Im Prinzip stellt auch das Videosignal eine serielle Form der Datenübergabe dar.

Nach dieser Definition können wir kurz auf eine Ein- und Ausgabemöglichkeit eingehen, deren dazugehörige Elektronik sich zwar nicht auf der Hauptplatine des Apple //e befindet, die aber trotzdem praktisch zum Standard gehört: gemeint ist hier die Ein- und Ausgabe zu einem oder mehreren Diskettenlaufwerken. Dieser Datentransfer funktioniert über eine Zusatzkarte in einem der Steckplätze. Der Datenaustausch zwischen dem Prozessor und der Zusatzkarte findet parallel, der Austausch zwischen der Zusatzkarte und einem angeschlossenen Diskettenlaufwerk findet seriell statt. Die Kontrolle der Ein- und Ausgabe zu den Diskettenlaufwerken erfordert ein sehr umfangreiches Programm, das bekannteste trägt den Namen DOS 3.3, die neueste Version eines Disketten-Betriebssystems ("Disk Operating System") hat einige erweiterte Möglichkeiten und heißt ProDOS.

Der Apple //e verfügt über elf serielle I/O-Ports, d.h. über elf serielle Ein- und/oder Ausgänge sowie über vier analoge Eingänge:

- Der *Lautsprecherausgang* ist eine serielle Verbindung, bei der jedes "Datenwort" tatsächlich nur aus einem einzigen Bit besteht;

- Die Ein- und Ausgänge zum *Kassettenrecorder* sind echte serielle Verbindungen - hier werden größere Datenmengen Bit für Bit übertragen, wobei die erforderliche Umwandlung über Routinen des Monitorprogramms geschieht;

- Die restlichen Ausgänge des Apple arbeiten alle mit TTL-Pegeln.<sup>7</sup>

In der rechten hinteren Ecke der Hauptplatine befindet sich ein 16-poliger IC-Sockel, der als *GAME I/O* bezeichnet wird. Er ist primär für den Anschluß von Joysticks mit dazugehörigen "Action-Tasten" gedacht, enthält darüber hinaus aber noch die folgenden Ausgänge:

- die "Announciators", insgesamt vier an der Zahl. Der elektrische Zustand der Announciators ("0" oder "1") kann über dazugehörige Softswitches gesetzt werden.

- den "Utility Strobe", einen Ausgang, der permanent den Pegel "1" hat. Durch Ansprechen eines dazugehörigen Softswitches wird ein Impuls vom 0,5 Mikrosekunden Dauer ausgelöst, d.h. der Ausgang geht für diese Zeit auf "0" und sofort danach wieder auf "1".

Außerdem enthält der GAME I/O noch sieben Eingänge:

- drei davon reagieren auf TTL-Pegel (d.h. 0 oder 5 Volt). Zwei dieser drei Eingänge werden normalerweise als Action-Tasten zusammen mit einem angeschlossenen Joystick verwendet. Diese beiden Eingänge sind mit den Tasten "offener Apfel" und "geschlossener Apfel" verbunden. Der dritte Eingang wäre normalerweise als erste Action-Taste zusammen mit einem zweiten Joystick verbunden, ein vierter Eingang (die zweite Taste für den zweiten Joystick) fehlt. Für diesen dritten Eingang gibt es ebenfalls eine Spezialfunktion: wenn auf der Hauptplatine die mit X6 bezeichnete Lötverbindung hergestellt wird, setzt jeder Tastendruck auf SHIFT diesen dritten Eingang. Der Trick war beim Apple II notwendig, damit ein Programm erkennen konnte, ob die Taste SHIFT gedrückt wurde, und wird als "Shift-Key-Modifikation" bezeichnet.

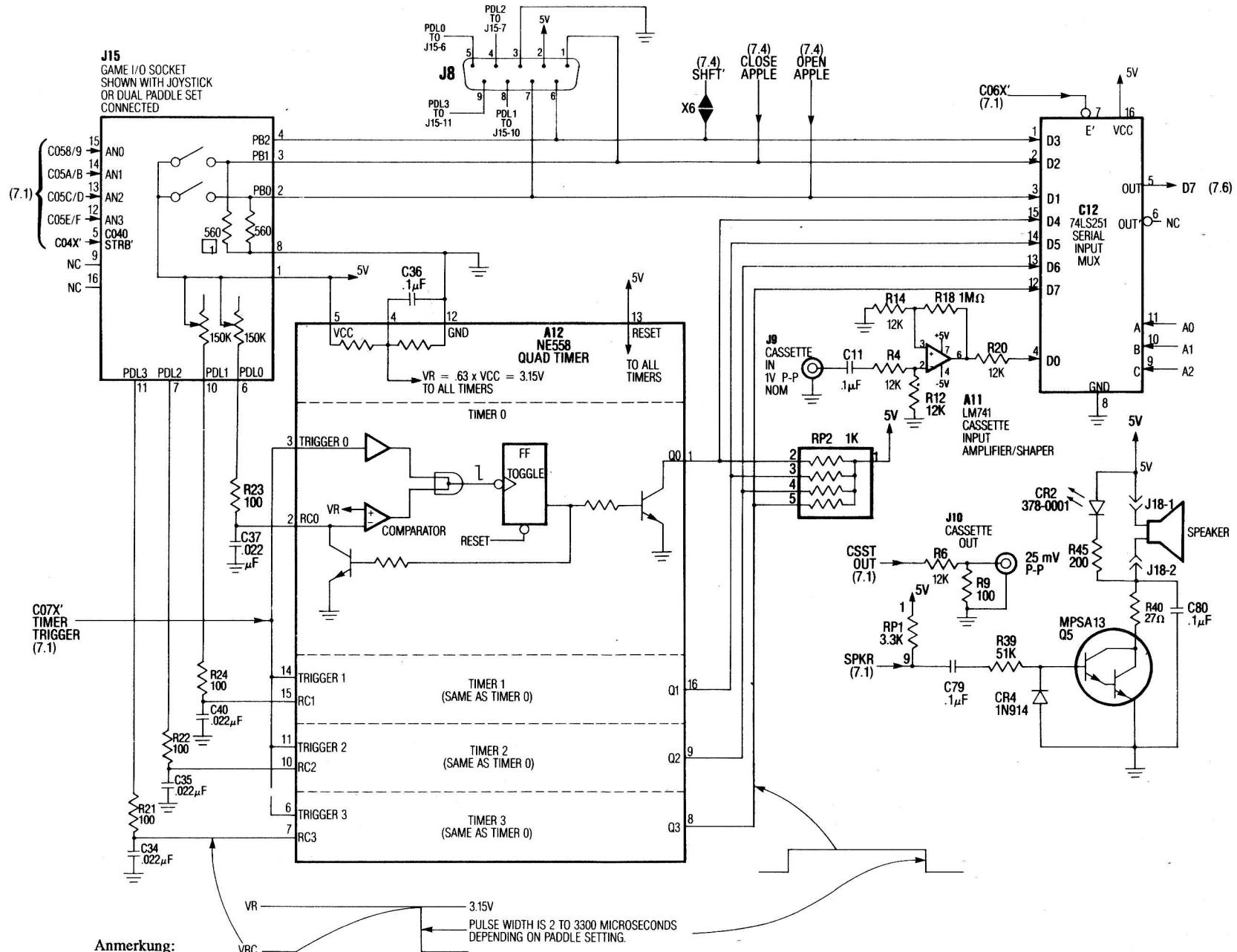

- die restlichen vier Eingänge reagieren nicht auf TTL-Pegel, sondern auf daran angeschlossene veränderbare Widerstände. An jeden dieser Eingänge kann ein *Paddle* bzw. an jeweils zwei dieser Eingänge ein Joystick angeschlossen werden. Beide Geräte enthalten nichts weiter als Potentiometer, also veränderbare Widerstände. Der Apple enthält dazu einen Zeitgeber mit einem Kondensator, der für jeden Lesevorgang aufgeladen und über einen angeschlossenen Widerstand wieder entladen wird. Je kleiner der Widerstand des Potentiometers ist, desto schneller geht die Entladung - je größer er ist, desto länger dauert es. Das Monitor-

<sup>7</sup> TTL steht für "Transistor-Transistor Logik" und damit für die Art und Weise, wie die meisten heutzutage käuflichen Chips kleinerer Dimension intern aufgebaut sind. Hochintegrierte Chips wie der 6502, die MMU und die IOU sind intern mit einer anderen Technik aufgebaut, sämtliche Ein- und Ausgänge halten sich aber ebenfalls an die TTL-Spezifikation: eine "0" wird durch einen Spannungswert zwischen 0 und 0,8 Volt, eine "1" durch einen Spannungswert zwischen 2,4 und 5 Volt dargestellt. Spannungen, die zwischen 0,8 und 2,4 Volt liegen, gelten als undefiniert.

programm enthält eine Routine, die diese Zeit mißt und darüber den Stand eines angeschlossenen Potentiometers feststellen kann. Ein Paddle enthält ein einziges, ein Joystick enthält zwei Potentiometer. Ein Potentiometer wird dabei durch horizontale, das andere durch vertikale Bewegungen des Joysticks eingestellt. Die Anwendungen sind dabei nicht auf Joysticks beschränkt - mit demselben Funktionsprinzip können ebenfalls Grafiktablets und andere Eingabegeräte angeschlossen werden.

Die vier Analogeingänge und die drei TTL-Eingänge für die Action-Tasten sind zusätzlich noch über einen unpoligen Steckverbinder auf der Rückseite des Gehäuses herausgeführt. Es ist demzufolge möglich, z.B. einen Joystick über diesen Steckverbinder anzuschließen und gleichzeitig noch ein anderes Gerät über die vom Joystick nicht belegten Anschlüsse des GAME I/O.

## Die Stromversorgung

Was hierzulande aus der Steckdose kommt, ist 220 Volt Wechselspannung, auf die ein Prozessor bestenfalls mit heftigen Rauchzeichen reagiert. Die hauptsächlich benötigte Spannung in einem Computer ist +5 Volt Gleichspannung, für die entsprechende Umwandlung ist das Netzteil zuständig.

Das Netzteil des Apple //e liefert vier Gleichspannungen: +5, +12, -5 und -12 Volt (bezogen auf die Masse des Systems). Diese Spannungen sind praktisch überall auf der Hauptplatine vorhanden und zu jedem Chip geführt, der sie benötigt. Außerdem haben alle Steckplätze außer dem speziellen Steckplatz eine Zuführung sämtlicher vier Spannungen, der spezielle Steckplatz stellt nur die Spannung +5 Volt zur Verfügung.

## Zusammenfassung

Der Apple //e ist ein Mikrocomputer mit einem Mikroprozessor des Typs 6502 und stellt eine Modernisierung und Erweiterung des Apple II dar. Auf der (einigen) Hauptplatine sind Speicher und Ein-/Ausgabefunktionen wie Tastatureingang und Videoausgang enthalten. Die Erweiterungen gegenüber dem Apple II schließen die Darstellung von Kleinbuchstaben, Bildausgabe mit 80 Spalten und eine Speichererweiterung von 48 bzw. 64 kByte auf 128 kByte ein (der Apple II verfügt nur über Großbuchstaben, 40 Spalten und 48 bzw. 64 kByte RAM).

Die Hauptplatine des Apple //e enthält sieben Erweiterungssteckplätze sowie einen speziellen Steckplatz und ermöglicht den fast beliebigen Ausbau des Computers. Eingesteckte Zusatzkarten sind mit den folgenden Signalen verbunden bzw. können diese Signale kontrollieren: IRQ', NMI', RESET' und DMA'. Über das Signal DMA' ist es einer Zusatzkarte möglich, den normalen Prozessor des Apple zeitweise oder vollständig von der restlichen Elektronik des Computers abzutrennen und an seiner Stelle einen anderen Prozessor einzusetzen.

Die Kontrolle sämtlicher Konfigurationsmöglichkeiten, Softswitches und Ein-/Ausgaben findet über Adreßdekodierung statt.

Von der Hauptplatine existieren zwei Versionen - die eine enthält einen Videogenerator, der Signale nach der amerikanischen NTSC-Norm generiert, der Videogenerator der anderen Version produziert Signale, die der europäischen PAL-Norm entsprechen.

Der Videoausgang kann direkt an einen monochromen oder farbigen Videomonitor oder einen Fernseher mit Videeingang angeschlossen werden. Über einen zusätzlichen HF-Modulator ist der Anschluß über den Antenneneingang eines normalen Fernsehers möglich, wenn auch nicht zu empfehlen.

Die Darstellung von Text kann in gemischter Groß- und Kleinschreibung erfolgen, die Zeichen sind mit einer 5 \* 7 Matrix aufgebaut. Alle verfügbaren 96 Zeichen können sowohl hell auf dunklem Hintergrund als auch dunkel auf hellem Hintergrund dargestellt werden, bei 64 dieser Zeichen ist zusätzlich blinkende Darstellung möglich (FLASH mit Kleinbuchstaben ist nicht definiert). Der verbesserte Apple //e enthält anstelle blinkender Großbuchstaben grafische Sonderzeichen ("Maus-Zeichensatz").

Der Apple //e wird in den jeweiligen Ländern mit einem entsprechenden Zeichensatz und einer national angepaßten Tastaturbelegung ausgeliefert, die bei Bedarf auf den amerikanischen Standard umschaltbar ist.

Im Modus TEXT sind bei einfacher Auflösung 40, bei doppelter Auflösung 80 Zeichen auf 24 Zeilen verfügbar.

Folgende Grafikmodi stehen zur Verfügung:

- LoRes40 mit  $40 * 48$  Blocks in 16 Farben;

- LoRes80 mit  $80 * 48$  Blocks in 16 Farben;

- HiRes40 mit  $140 * 192$  Punkten in 8 Farben bzw.  $280 * 192$  Punkten schwarzweiß;

- HiRes80 mit  $140 * 192$  Punkten in 16 Farben bzw.  $560 * 192$  Punkten schwarzweiß.

Die doppelt auflösenden Modi sind nur mit einer 80-Zeichen-Karte im speziellen Steckplatz möglich, die doppelt hoch auflösende Grafik nur dann, wenn die 80-Zeichen-Karte über zusätzliche 64 kByte RAM verfügt.

Die Tastatur des Apple //e besteht aus 63 Tasten, deren Belegung zwischen dem amerikanischen Standard und einem nationalen Zeichensatz umschaltbar ist. Sie enthält zusätzliche Funktionen wie Autorepeat und N-Key Rollover und ist somit für die meisten denkbaren Anwendungen geeignet. Zusätzlich ist auf der Hauptplatine ein separater Steckverbinder für die Installation eines numerischen Zehnerblocks vorhanden.

Der 6502-Prozessor des Apple //e arbeitet mit 1.0205 MHz.

Die Hauptplatine enthält 65536 Byte dynamischen RAM und ist für die Kontrolle und Versorgung weiterer 65536 Byte RAM auf einer Zusatzkarte im speziellen Steckplatz eingerichtet. Innerhalb von 16 kByte Firmware befinden sich die Programmiersprache Applesoft BASIC, das Monitorprogramm und zusätzliche Routinen für den Betrieb mit 80 Zeichen.