the practical introduction to a powerful system

Book 2

Elektor

# The Elektor Junior Computer

the practical introduction to a powerful system

A.Nachtmann G.H.Nachbar

Elektor Publishers Ltd.

#### Copyright © 1981 Elektor Publishers Ltd. - Canterbury.

The contents of this book are copyright and may not be reproduced or imitated in whole or in part without prior written permission of the publishers. This copyright protection also extends to all drawings, photographs and the printed circuits boards.

The circuits published are for domestic use only. Patent protection may exist with respect to circuits, devices, components etc. described in this publication. The publishers do not accept responsibility for failing to identify such patent or other protection.

Printed in the Netherlands ISBN 0905705076

### Feeling peckish?

How are you enjoying the Junior Computer so far? Everything to satisfaction? Fine. In that case, you must be eager to digest Book 2, a complete menu of computer facts and programming material.

Dig in, folks!

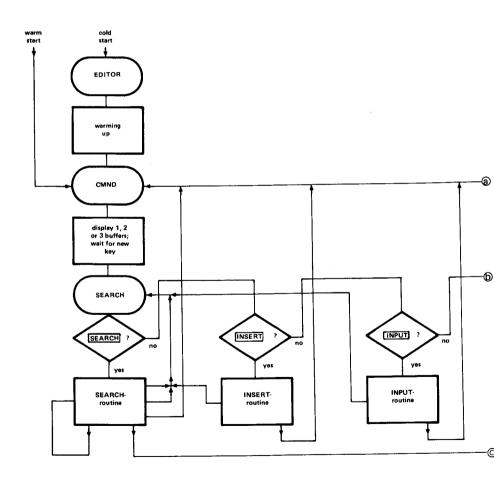

Now that we've got the Junior Computer up and running (Book 1) it is time to construct and construe a number of 'tools' with which to operate the microprocessor as efficiently as possible.

This is where chapter 5 comes in. It presents the programmer with such essential tools as the 'editor' and the 'assembler'. These are highly effective as they enable typing errors to be corrected and additional instructions to be inserted at any point without having to re-enter the entire program. The programmer now no longer has to calculate displacements (during conditional branch instructions and absolute addresses (during jump instructions) himself: all these tiresome chores are dealt with automatically inside the Junior Computer's EPROM.

Chapter 6 teaches the Junior Computer to 'sing'. It includes several circuits which, together with the peripheral interface adapter (PIA), turn the JC into a keyboard instrument. Via the PIA the computer controls a loud-speaker and in Book 3 it will be seen to use the same method to operate a printer.

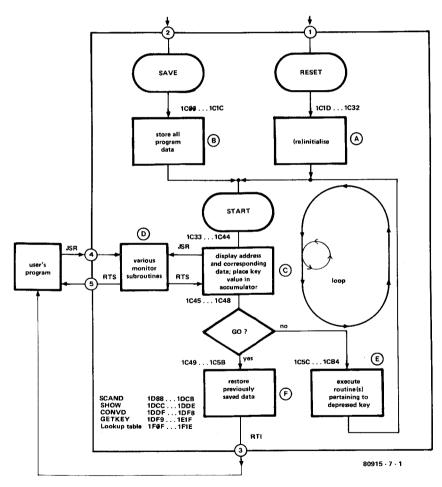

The remaining chapters (7, 8 and 9) provide a detailed description of the monitor, the editor and the assembler, respectively, all of which combine to form the EPROM brain. Once the user knows exactly how the Junior Computer 'ticks', he/she will be able to write suitable programs personally. Various subroutines introduced in the book will then be of great assistance.

Finally, the appendix gives a clear and coherent summary of all the available subroutines and listings.

After reading Book 2 and mastering the contents, the programmer will be ready to add a printer and a cassette interface to the standard Junior Computer. These peripheral devices, to be 'served up' in Book 3, will transform

| the | machine    | into   | а | full-fledged  | personal  | computer.   | Then | the | Junior |

|-----|------------|--------|---|---------------|-----------|-------------|------|-----|--------|

| Con | nputer wil | I have | w | ell and truly | 'outgrown | ' its name. |      |     |        |

The authors.

P.S. Since nothing in this world is perfect — including the Junior Computer! — we will lend a willing ear to any suggestions or comments that readers might care to make.

### **Contents**

| Chapter 5                    |

|------------------------------|

| The Editor and the Assembler |

| Chapter 6                    |

| Chapter 7                    |

| Chapter 8                    |

| Chapter 9                    |

| Appendix 1                   |

| Appendix 2                   |

## The Editor and the Assembler

Typing in a program is a dull, irksome occupation. As was shown in Book 1, each individual instruction has to be entered, one byte at a time. But before this can be done, a fair amount of paper work is involved:

- subroutine start addresses.

- displacements inherent to conditional branch instructions and

- absolute addresses inherent to unconditional branch instructions (jump instructions) all have to be calculated first.

When the entire program has finally been entered into the computer, it has to be checked for typing errors. Supposing one byte happened to be left out somewhere in the middle of the program. Does this mean retyping the whole lot? No — thanks to the editor and the assembler — it doesn't!

The editor and the assembler are both stored inside the Junior Computer's EPROM. The former allows new instructions to be inserted at any given point in the program, even after entry; in addition, it tracks down instructions and, if necessary, deletes them. Thus, the keyboard and the editor act as a 'pencil and rubber', so to speak, while data is being entered.

The editor also permits the programmer to type in symbolic addresses, called 'labels'. After this, the assembler steps in to calculate subroutine start addresses, displacements in the event of conditional branch instructions and absolute addresses for jump instructions, and all without any human help! As a result, program errors are reduced to a minimum and the user is saved a great deal of unnecessary labour.

#### The Editor

Having studied the Junior Computer Book I, you should be familiar with most of the instructions and address modes appertaining to the 6502 microprocessor. Various program examples were given which showed how easy it is to program the JC. Up to now the data entered consisted entirely of hexadecimal numbers. When the AD key was depressed the JC 'knew' it had to interpret the following key information as addresses. Pressing the DA key, on the other hand, told it to store any entered data in the actual address location displayed.

As far as short programs are concerned, such as those given in Book I, this type of data entry is quite adequate. When more extensive programs are involved however (with a length of, say, several hundred bytes), typing errors can occur frequently and correcting them can become a very tedious procedure. What do you do, for instance, if a few instructions have been omitted from the middle of the program? Normally, this would mean having to re-enter a large part of the program from the correction onwards. What a waste of time and effort! Redundant instructions can be removed by replacing them with NOP instructions (op-code EA), which is making very poor use of the computer's memory space. Think how irritating it would be, if, when entering a long program, you run out of memory!

Fortunately, this can now be avoided with the aid of one of the JC's greatest assets: the EDITOR. This enables bytes to be inserted or deleted anywhere within the memory area. When bytes are to be inserted, the computer makes room for them by moving a data block further down in the program. When bytes are to be deleted, the data block is moved up to 'close the gap'. Block transfers and their respective programs were mentioned in Book I during the description of indexed and indirect addressing.

In short, the editor can save a lot of time and trouble where program correction is concerned. Exactly how simple it is to enter and correct programs will be seen later on in this chapter.

#### The Assembler

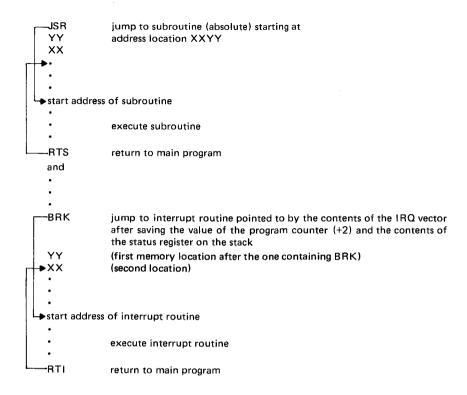

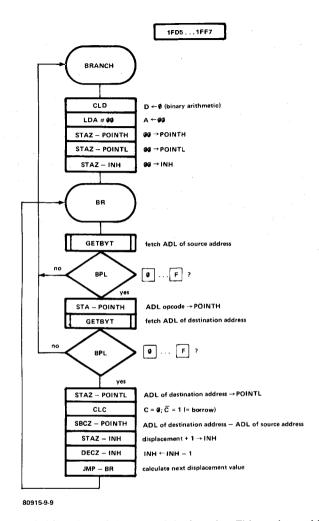

Another indispensable aid towards simple, error-free, high-speed program entry is the assembler. As you will remember from Book I, branch instructions are often used. Before the displacement value of a branch instruction can be calculated, it is important to know the start and destination addresses. It is only then that the monitor routine BRANCH (start address 1FD5) can calculate the displacement. The same applies to the instructions JSR and JMP — the true jump address must be known. Thus, before a program can be keyed in, you must be familiar with the absolute addresses of the branch and jump instructions. Obtaining the correct addresses numerically involves a great deal of writing. A more efficient method is to let the assembler in the monitor program take care of it.

It fulfils the task quickly and simply and, above all, accurately. All that is required is to depress the GO key and the computer will calculate all the displacement values, absolute addresses of jump instructions and the subroutine start addresses by itself. Incredible as it may seem, the JC takes this painstaking job off the programmer's hands and completes it in a

matter of seconds. What is more, the assembler, the editor and several other routines only occupy 1 k of EPROM! This is possible as the 6502 microprocessor happens to have highly effective and powerful instructions and numerous address possibilities.

The time has now come to take a closer look at the editor and assembler and find out exactly how to use them.

#### Editing and assembly from start to finish

Before the editor and assembler can be put into operation, we need to develop a program to be run on the Junior Computer. The program should perform the following:

- convert an 8-bit binary number into decimal

- display the binary number in hexadecimal form next to the decimal figure

- use the keyboard to enter the hexadecimal number

- use monitor routines to scan the six digit display.

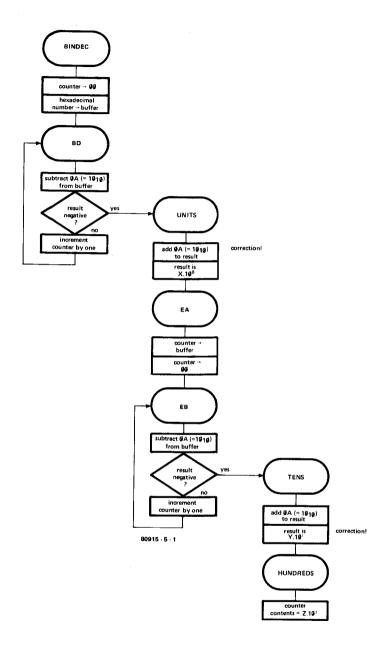

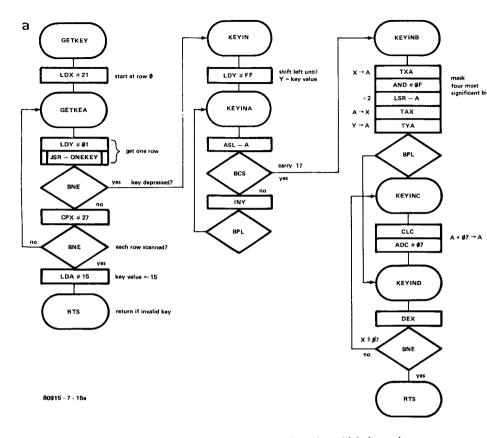

The object of the exercise is to write a program as quickly as possible, free of errors and which meets the above requirements. It is best to start by constructing an algorithm which outlines the conversion of an 8-bit binary number  $(\emptyset\emptyset \ldots FF)$  into decimal  $(\emptyset 1 \emptyset \ldots 2551 \emptyset)$ . This is shown in figure 1. As can be seen, the algorithm is expressed in words. It should be mentioned at this stage that it is always a good idea to write down a complicated program in words first! Then a rough flow chart can be produced leading to the actual program.

During the binary to decimal conversion program, BINDEC, a counter is reset to zero and the hexadecimal number to be converted is stored inside a buffer. The actual procedure is as follows:

- 1. The value ØA (=1010) is repeatedly subtracted from the hexadecimal number in the buffer until the buffer contents become negative. After each subtraction the counter is incremented by one. This means that in the end the counter will show how many subtractions were carried out before the result became negative.

- 2. In order to represent a negative 8-bit number in an 8-bit processor, a 16-bit buffer is required consisting of two memory locations.

- 3. If the most significant digit of the 16-bit number is a 'one', the result of the subtraction was negative and the program branches to the section labelled UNITS. Here the processor will add ØA to the negative buffer contents. The result is a figure which can assume a value between Ø...9 and is the number of units of the decimal answer.

- 4. The contents of the counter are stored in the 16-bit buffer, after which the counter is once again reset. The processor will now continue to subtract ØA from the buffer contents until a negative result is obtained. The counter will again indicate the number of subtractions that were carried out.

- 5. When ØA is then added to the negative buffer contents, a figure is obtained which can assume any value between Ø...9 and which represents the tens of the decimal answer.

- The counter will now contain a figure with a value from Ø...2, representing the hundreds of the decimal answer.

Figure 1. Before we can work with the editor and the assembler, let us develop a program that converts a hexadecimal value into a decimal. The editor and the assembler will be seen to intervene as soon as the program is written in memory. The flow chart contains a conversion algorithm.

This is all very well in theory, but of course only a practical example can prove that the algorithm really works. Let us therefore convert the hexadecimal value 0091 into decimal in the same way as the program given in figure 1.

| number buffer:  | ØØ91<br>ØA   | counter: ØØ       |

|-----------------|--------------|-------------------|

| number buffer:  | ØØ87<br>- ØA | counter: Ø1       |

| number buffer:  | ØØ7D<br>– ØA | counter: Ø2       |

| number buffer:  | ØØ73<br>– ØA | counter: Ø3       |

| number buffer:  | ØØ69<br>- ØA | counter: Ø4       |

| number buffer:  | ØØ5F<br>– ØA | counter: Ø5       |

| number buffer:  | ØØ55<br>– ØA | counter: Ø6       |

| number buffer:  | ØØ4B<br>- ØA | counter: Ø7       |

| number buffer:  | ØØ41<br>- ØA | counter: Ø8       |

| number buffer:  | ØØ37<br>- ØA | counter: Ø9       |

| number buffer:  | ØØ2D<br>- ØA | counter: ØA       |

| number buffer:  | ØØ23<br>- ØA | counter: ØB       |

| number buffer:  | ØØ19<br>- ØA | counter: ØC       |

| number buffer:  | ØØØF<br>- ØA | counter: ØD       |

| number buffer:  | ØØØ5<br>– ØA | counter: ØE       |

| negative result | (- ØØØ5)     | counter unchanged |

When  $\emptyset A$  is added to the negative number contained in the buffer the result will be 5 once more. This will be the number of units contained in the decimal answer. Thus,  $91_{16} = ZY 5_{10}$ .

The contents of the counter (ØE) are now transferred to the number

buffer and the counter is once more reset. The new buffer contents are then worked on to provide the next number:

number buffer:

ØØE counter:

ØØ

ØA

number buffer:

ØØØ4 counter:

Ø1

ØA

negative result

( ØØØ6) counter unchanged

When  $\emptyset A$  is added to the negative number contained in the buffer the result will be 4 once more. This will be the number of tens contained in the decimal result. Thus, 9116 = Z 4510.

The counter contains 1, which represents the number of hundreds in the decimal result. The complete answer is therefore: 91<sub>16</sub> = 145<sub>10</sub>. The methods used to present this figure to the computer's display were described in Book I.

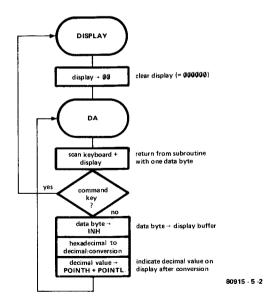

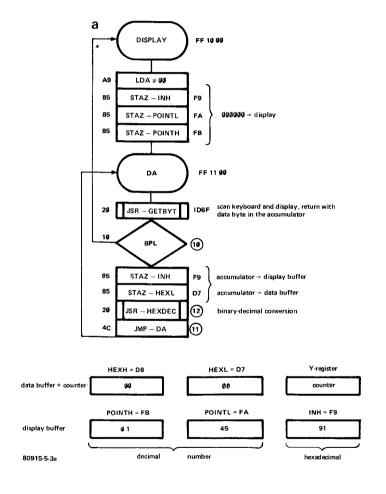

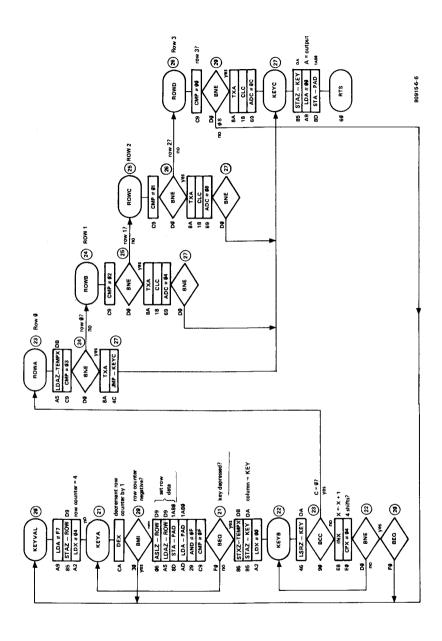

Now the algorithm for the binary to decimal conversion program is ready and the rough flow chart can be drawn up, as shown in figure 2.

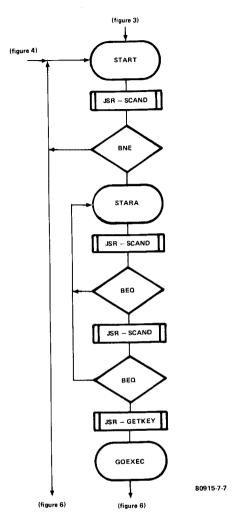

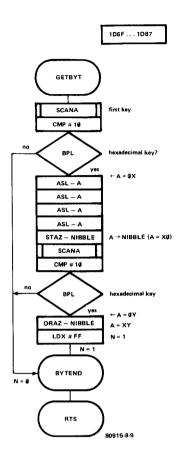

Firstly, the display buffer is cleared. The computer then scans the keyboard and the display. The subroutine which the main program requires was also dealt with in Book I, subroutine GETBYT (start address 1D6F). If a command key is depressed, the processor will reset the N-flag before returning to the main program. In this way, the display can be cleared whenever a command key (it doesn't matter which) is depressed.

Figure 2. The general flow chart required to control the display and scan the keyboard during the hexadecimal to decimal conversion.

Once the two data keys have been depressed, the microprocessor returns from the GETBYT subroutine with the entered data byte in the accumulator. This data byte is then transferred to the display buffer INH. It is at this point that the binary-to-decimal conversion takes place according to the algorithm drawn up previously. The decimal number obtained is also transferred to the display buffers POINTH and POINTL.

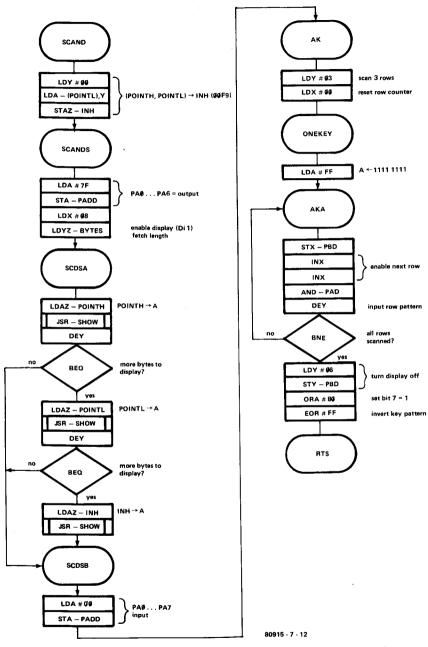

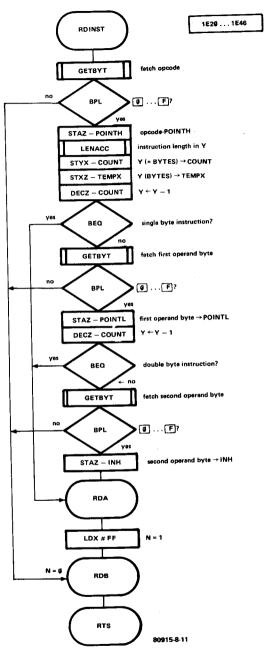

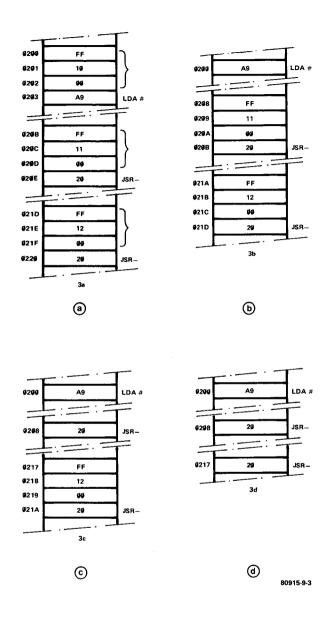

Once again, the computer will scan the keyboard and display the hexadecimal and the decimal numbers via the GETBYT subroutine. The full details of the flow chart are given in figure 3. The display buffer consists

Figure 3a. The detailed version of the flow chart in figure 2. The display buffer INH contains the hexadecimal value that is to be converted. After the conversion, the decimal number will be stored in display buffers POINTH and POINTL. Memory locations HEXH and HEXL and the Y index register act as temporary memory banks.

of addresses 00F9...00FB. The data or number buffer occupies addresses 00D7 and 00D8. The memory locations reserved for the program can be labelled as follows:

INH \* \$ ØØF9

POINTL \* \$ ØØFA display buffers

POINTH \* \$ ØØFB HEXL \* \$ ØØD7

HEXH \* \$ 00D8 data buffers

GETBYT \* \$ 1D6F monitor subroutine

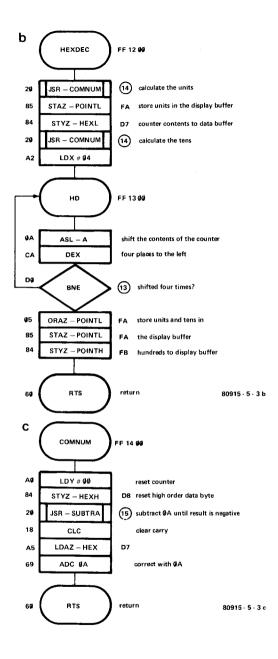

During the program the Y register will be used as a counter instead of a memory location. As can be gathered from figure 3, the main program DISPLAY contains the two subroutines GETBYT and HEXDEC. Both are different in that the start address of GETBYT is known, whereas that of HEXDEC is not. This is no problem, as from now on the computer will be able to calculate start addresses by itself. Thus, there is no need to assign a start address to HEXDEC. In addition, the main program includes a jump and a branch instruction. The destination address for the jump instruction and the displacement value for the branch instruction are also calculated by the computer, so that there is no need for the programmer to worry about them either.

The subroutine HEXDEC, which is the practical version of the algorithm we developed before, incorporates two subroutines, COMMUN and SUBTRA, as well as jump and branch instructions. Here again, we needn't worry about which addresses belong to which subroutines and what displacement values are required for the branch instructions. These tiresome, time-consuming calculations can all be left to the computer to deal with, which, after all, cannot go wrong!

The section of the monitor program which calculates the displacements of branch instructions is called the assembler. It is started in the usual manner, at address 1F51, by depressing the GO key.

For the assembler to function properly, the computer requires a tool to prepare the programs so that the assembler can 'digest' them. This tool is in fact the editor.

As we mentioned before, the computer calculates addresses and displacements by itself. The question is: how does it know where to jump or branch, if the programmer does not enter the start or destination addresses? Well, the programmer simply enters symbolic addresses into the computer. From now on it is enough to enter JSR-SUBTRA, instead of JSR-023B, for they both mean the same thing as far as the JC is concerned! Thus, the assembler's task consists of allocating the absolute address Ø23B to the symbolic address SUBTRA. However, the word SUBTRA cannot be entered into the JC, as the only means of entering data is the hexadecimal keyboard — there is no alphanumeric one at the present time. This means that a label may only consist of hexadecimal characters which could, if we are not careful, be interpreted as op-codes or operands. The computer must therefore be able to distinguish between op-codes and labels. What in fact is the difference between them? To find out, look at the appendix to Book I where the op-codes of the 6502 microprocessor have been compiled in hexadecimal sequence. As the table shows, not all the hexadecimal

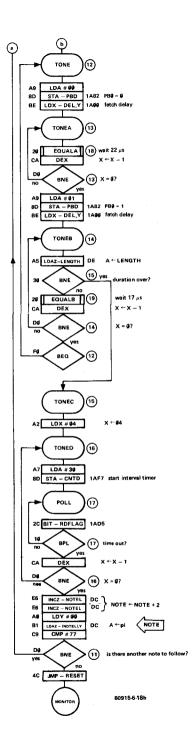

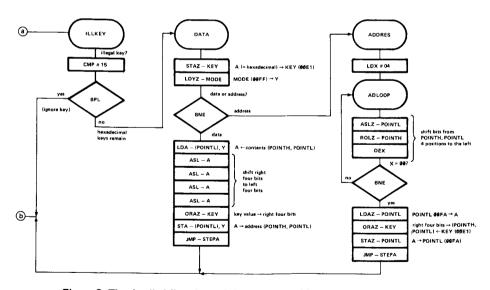

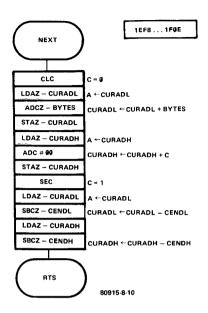

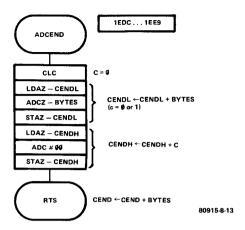

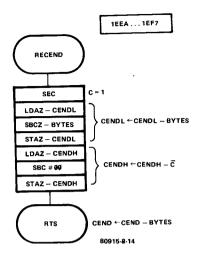

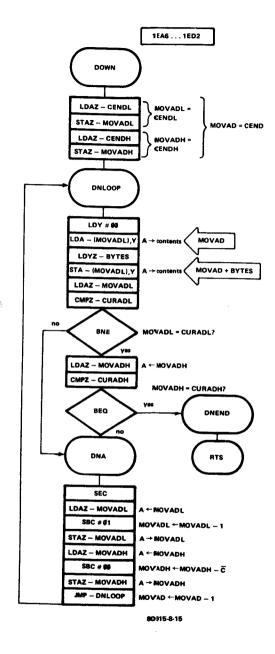

Figures 3b and 3c. The actual hexadecimal to decimal conversion takes place in the course of the HEXDEC subroutine. The COMNUM routine first calculates the units, then the tens and finally the hundreds.

Figure 3d. During the subroutine SUBTRA the processor carries out a 16 bit subtraction. The hexadecimal number ØA is subtracted several times until it gives a negative result. Here the Y index register acts as a subtraction counter.

numbers from  $\emptyset\emptyset$ ... FF have been allocated op-codes. There are several gaps. Even the hexadecimal number FF has no op-code. Let us give it a pseudo op-code, in other words, an op-code unknown to the microprocessor. Now the hexadecimal number FF can be used as a label. We could have chosen any other unused number from the table, such as  $\emptyset4$ , D3 or F7, but FF happens to be the easiest to enter.

The label SUBTRA still has a few other aspects worth considering. SUBTRA is the program departure point, or to be more exact, the symbolic start address of a subroutine. The pass-word to call up the subroutine is JSR-SUBTRA (jump to subroutine SUBTRA). Since only hexadecimal figures are used in the editor, subroutine SUBTRA will have to have a number. This can be any number from  $\emptyset\emptyset$ ... FF. Up to 256 such labels can be used for identification purposes in a program.

It is now high time to put the above into practice with the aid of a few examples, for from now on program entry will always involve the editor and the assembler contained in the monitor program.

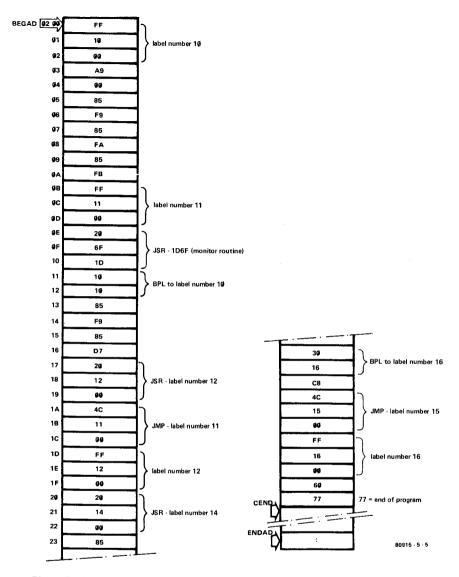

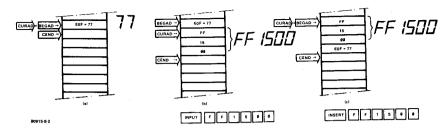

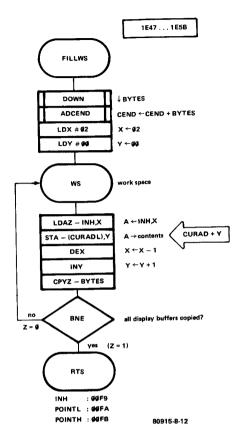

Figure 4. This is how the editor stores the initial instructions pertaining to the DISPLAY program (figure 3a) in the Junior Computer's memory. BEGAD and ENDAD are pointers and define the work space.

#### The Editor

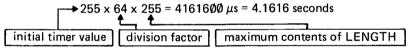

#### 1. Structure of a label:

FF 15 ØØ example

FF XX ØØ general pattern

label indicator label number label limiter

As can be seen a label is three bytes long. In order to enter a label into the JC, six keys will have to be depressed. Figure 3 shows that the label SUBTRA is replaced by FF 15 00. Once the editor has been activated, labels like this can be entered straight into the computer. An ASCII keyboard (typewriter) will not be necessary.

Other valid entries include:

keyboard display

FF 37 00 FF 37 00 label number 37

FF FA 00 FF FA 00 label number FA

FF 00 00 FF 00 00 label number 00

Non-valid label entries include:

keyboard display

FF 21 FF 21 XX limiter missing

FF 21 FF 21 XX limiter missing FF 56 FF FF 56 FF wrong limiter FF FF 41 00 although the

although the correct limiter will appear in the display after the label entry, it must be overwritten with M0

Once the entire label entry has been completed, the display buffer is copied into the memory.

2. Structure of a JSR instruction:

20

14

00

example

20

XX

00

general pattern

op-code of JSR subroutine number limiter

As usual, the jump to subroutine instruction is three bytes long. Now let us return to figure 3. During the HEXDEC subroutine, COMNUM is called twice. Usually, the instruction would be written as JSR-COMNUM. Subroutine COMNUM has been given the label number 14, but any other number would have been equally suitable. To the computer, 20 14 00 means: jump to subroutine number 14, or to put it more precisely: jump to the subroutine which starts with the label number 14. As you will remember, FF 14 00 and COMNUM are the same in the flow chart.

Other valid entries for a JSR instruction include:

keyboard display

20 39 00 20 39 00 jump to subroutine 39 20 9A 00 20 9A 00 jump to subroutine 9A 20 20 00 20 20 00 jump to subroutine 20

Non-valid JSR entries include:

keyboard display

20 11 20 11 XX limiter missing 20 71 9F 20 71 9F wrong limiter 20 20 28 00 although the ri

although the required subroutine number and the correct limiter appear in the display, this is a *coincidence* and the entire instruction must be entered. Only then will the display buffer be copied into the memory of the computer.

3. Structure of a jump instruction:

op-code of JMP instruction label number limiter

The jump instruction is also three bytes long. Towards the end of the main routine DISPLAY, a jump instruction can be seen, JMP-DA, or jump to label DA. The JC interprets 4C 11 00 as: jump to label number 11. Again, labels DA and FF 11 00 are the same.

Other valid entries for a jump instruction include:

keyboard display

4C 77 ØØ 4C 77 ØØ jump to label number 77 4C 29 ØØ 4C 29 ØØ jump to label number 29 4C ØØ ØØ 4C ØØ ØØ jump to label number ØØ

Non-valid jump entries include:

keyboard display

4C 4C 24 00 again, the complete instruction must be entered before the computer will copy it into the memory

The hexadecimal numbers following the JSR and JMP instructions do not therefore constitute absolute addresses, but label numbers which the

programmer is free to select. The true absolute addresses to be jumped to are calculated by the computer during assembly. The JSR and JMP instructions are three bytes long and require the limiter byte  $\emptyset\emptyset$ . This fact must be taken into account during program entry.

#### 4. Structure of a branch instruction:

The 6502 microprocessor features eight branch instructions: BCC, BCS, BEQ, BMI, BNE, BPL, BVC and BVS with the op-codes 90, BØ, FØ, 30, DØ, 10, 50 and 70 respectively. The displacement values for these instructions are calculated by the assembler in the monitor program. A branch instruction entry has the following structure:

30 16 example 30 XX general pattern

op-code of BMI instruction label number

Other examples of branch instruction entries are:

9Ø 34 BCC to label number 34 BØ F6 BCS to label number F6 FØ 19 BEQ to label number 19 3Ø 56 BMI to label number 56 DØ 9D BNE to label number 9D

10 21 BPL to label number 21

50 A3 BVC to label number A3

70 EA BVS to label number EA

Thus, the numbers following the branch instructions are not displacements, but label numbers which the programmer can select at will. The true displacements are calculated by the JC during essembly. Branch instructions are two bytes long and so do *not* require the limiter byte  $\emptyset$ 0.

#### 5. Further points to consider:

During program entry in the editor mode care should be taken to define label numbers unambiguously. This means that a certain label number may only be used *once*. The label numbers may be entered in any sequence. Where the entry of branch instructions is concerned, it is important to make sure that the range (-128...+127) is not exceeded, for if this happens, the assembler will not report the error, but will calculate the *wrong* displacement.

#### 6. JMP, JSR and their defined addresses:

In many cases, a JMP or JSR instruction will lead to a definite address. In other words, the computer is *not* supposed to assemble the instruction. In figure 3 the computer is shown to jump from the main program to the subroutine GETBYT at address 1D6F. This address is established by the monitor program and may not change during assembly! To prevent such instructions from being assembled, a safeguard has been built into the assembler.

Example: JSR-GETBYT = 20 6F 1D op-code of JSR ADL ADH

The low-order address byte (ADL) belonging to the JSR instruction is

<sup>\*</sup>A JMP or JSR instruction will only be assembled if a label number is attached to it.

<sup>\*</sup>A JMP or JSR instruction will *not* be assembled if its label number is ambigiuous (already in use).

6F. The label number 6F does not appear in the program (figure 3) and so the assembler will not assign an address to the JSR-GETBYT instruction but will ignore it.

#### 7. Entry of the remaining instructions:

Taking the load instruction (LDA) as an example:

| keyboard    | display  | mnemonic   | address mode          |

|-------------|----------|------------|-----------------------|

| A 9 7 F     | A9 7F    | LDA 7F     | immediate             |

| A D 8 2 1 A | AD 82 1A | LDA-1A82   | absolute              |

| A 5 E 6     | A5 E6    | LDAZ-E6    | zero page             |

| A 1 F A     | A1 FA    | LDA-(FA,X) | pre-indexed indirect  |

| B1FA        | B1 FA    | LDA-(FA),Y | post-indexed indirect |

| B D Ø Ø Ø 2 | BD ØØ Ø2 | LDA-0200,X | absolute indexed, X   |

| B 9 D 1 2 2 | B9 D1 22 | LDA-22D1.Y | absolute indexed, Y   |

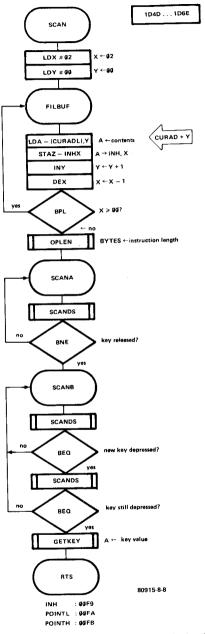

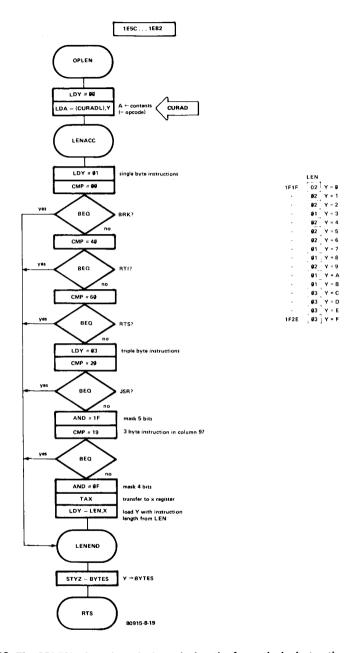

| B 5 3 1     | B5 31    | LDAZ-31.X  | zero page indexed,X   |

The validity of the above also holds for the remainder of the 6502 instructions. The computer will calculate the length of each instruction by itself. For this it will use the monitor subroutine OPLEN which is almost identical to LENACC described in Book I. It enables the computer to control the display irrespective of the instruction length. As you know, instructions that use implied addressing are only one byte long. For this reason only the op-code field of the display will be lit when these instructions are entered. The rest of the display will be 'blanked'.

Instructions belonging to the above category have *no symbolic addresses* allocated to them. That is to say, the programmer must define the address locations from which data is to be read out or to which data is to be written, before the program can be entered.

#### 8. Definition of program memory space:

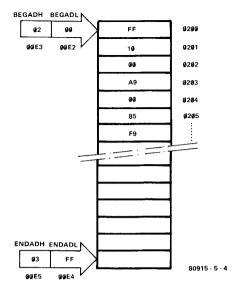

Before the editor can be activated, the memory space required for storing the program must be defined. The boundaries are determined by two address pointers located on page zero. The pointer BEGADH, BEGADL (= BEGin ADdress High, BEGin ADdress Low) is stored in locations:

BEGADL \* \$ 00 E2 BEGADH \* \$ 00 E3

The pointer ENDADH, ENDADL (= END ADdress High, END ADdress Low) is stored in locations:

ENDADL \* \$ 00 E4 ENDADH \* \$ 00 E5

BEGAD therefore always refers to the initial address and ENDAD to the final address of the memory area in which the program is to be stored.

Two consecutive pages of memory, page 2 and page 3, are available in the standard version of the Junior Computer. This amounts to 512 bytes, which should be ample for most programs. It is therefore a good idea to define this large area of memory space by means of the address pointers before entering a program:

BEGADH, BEGADL = Ø2 ØØ and ENDADH, ENDADL = Ø3 FF

The relevant data can be entered into these pointers via the keyboard as follows:

#### AD Ø Ø E 2

| DΑ | ØØ  | ADL of the BEGAD pointer |

|----|-----|--------------------------|

| +  | Ø 2 | ADH of the BEGAD pointer |

| +  | FF  | ADL of the ENDAD pointer |

| +  | Ø 3 | ADH of the ENDAD pointer |

The pointers are located on page zero and the memory area in which the program is to be run can be defined as 0200...03FF. Other areas of memory can also be 'fenced off' in the same manner.

Page Ø \$ ØØØØ ... ØØEØ Page 1 \$ Ø1ØØ ... Ø1F2 Page 1A \$ 1AØØ ... 1A79

There is only a limited amount of memory space available on these pages as they are partly occupied by the monitor program and the stack. If the limits of these areas are exceeded, the JC will report this as an error: EEEEEE.

#### 9. How to start the editor:

Once the required memory space has been defined, the editor can be put into operation. The start address is 1CB5 and it can be initiated by depressing the following keys:

AD1CB5

GO

The op-code portion of the display will now show 77 and the operand area of the display will remain blank. This is the computer's way of telling you that the editor is functioning and is ready to store any instructions entered inside the pre-determined operational memory area (work space).

#### 10. Editor command keys:

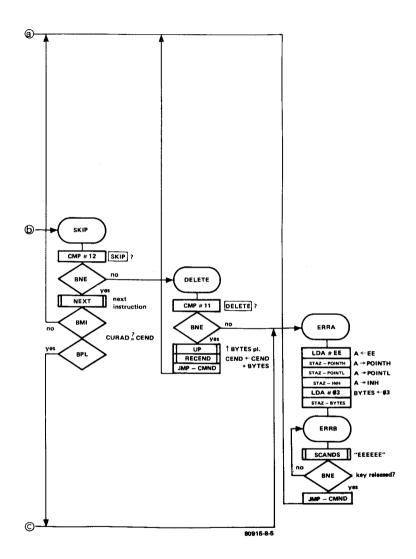

As soon as the editor is activated, the functions DA, AD, +, PC and GO are no longer valid. From now on, the second heading associated with these keys (SEARCH, INPUT, INSERT, DELETE and SKIP) will become effective. These keys enable instructions to be entered into the computer (INSERT, INPUT), to be deleted (DELETE) or even to be searched for (SEARCH). In addition, it is possible to jump from instruction to instruction via the SKIP command. Let us now examine each command in turn.

#### INSERT

The INSERT command allows a new instruction to be inserted before the one indicated on the display.

Whenever the pseudo-instruction 77 appears on the display the INSERT key must be depressed *without fail* for the data to be entered as instructions. The INSERT key is therefore the first key to depress if a label or an instruction is to be entered into the computer, once the editor has been activated.

#### INPUT

The INPUT command enables a new instruction to be entered after the one indicated on the display.

The programmer can select between the INPUT and INSERT commands at all times. Whichever key was the last to be operated will then be valid. As far as both are concerned, it should be noted that when they are used to

enter labels or instructions, the following data will be shifted into the display buffer one byte at a time. Only when the entire instruction has been entered into the computer will it be copied from the display buffer into the pre-determined memory area. This means that if an error occurs when entering an instruction, either the INSERT key of the INPUT key must be depressed several times before the error can be corrected. INSERT will place the fresh instruction in front of the one previously displayed, whereas INPUT will place it behind that instruction. Thus, each key will retain its proper function. The result is a simple, yet highly effective procedure to enter and edit programs.

#### DELETE

The DELETE command enables the displayed instruction to be erased from memory.

The computer will fill up the memory locations which have now become available. This is done by transferring (shifting) the data block immediately following the erased instruction upwards by the number of bytes deleted. It ensures that no 'gaps' occur in the program once an instruction is deleted. In other words, the instruction following the one just deleted will appear on the display as soon as the DELETE key is pressed. Again, by repeatedly depressing the INSERT or INPUT keys, new instructions can be entered before or after the instruction shown.

#### SEARCH

The SEARCH command enables the computer to look for (and find) any double-byte pattern in the memory area.

If, for example, we depress the keys SEARCH FF 11, the computer will search for label number 11 and show it in the display. The SEARCH command also manipulates the display pointer CURAD, also located on page zero, which always points to the op-code currently on display. This pointer is held in the following memory locations:

CURADL \* \$ ØØ E6 CURADH \* \$ ØØ E7

Initially, the SEARCH command leads the display pointer CURAD to the start address of the previously defined memory area. Since each instruction has a certain, specific length, calculated by the computer, CURAD is moved from op-code to op-code (and not from memory location to memory location). Through a set of simple comparisons, the computer can establish whether or not the required bit-pattern has been found. Labels are not the only things that can be searched for in this manner, any other type of instruction can also be located; for example:

SEARCH A9 ØØ,

SEARCH 4C 11 (figure 3) or

SEARCH 69 ØA (figure 3).

Note that if the same instruction occurs more than once in a program, the SEARCH command will only locate the first of them (the instruction nearest the start of the memory area). In other words, it is unable to discover two identical instructions in a row!

#### SKIP

The SKIP command enables the computer to jump from instruction to instruction.

This command is used to run through a program step by step, so that it can be checked for any errors in a matter of seconds.

Note: The INPUT command is essentially a combination of the SKIP and INSERT commands. This creates the following analogies:

```

SKIP INSERT X X = INPUT X X (1 byte)

SKIP INSERT X X X X = INPUT X X X X (2 bytes)

SKIP INSERT X X X X X X = INPUT X X X X X X (3 bytes)

```

11. Cold start entry/Warm start entry:

There are two start addresses for the editor:

Cold start entry = 1CB5 and Warm start entry = 1CCA.

If the editor is started at the former address, it will add (and initialise) a few pointers to page zero outside the memory area chosen by the programmer. Thus, before a program can be entered for the first time, the editor must be started at address 1CB5.

Warm start entry, on the other hand, makes it possible for the programmer, to return to the editor after depressing the RST key. In this case, the pointers on page zero will not be initialised. After starting the editor at address 1CCA, the command keys INSERT, INPUT, DELETE, SEARCH and SKIP will operate in their usual manner.

12. How to enter the program shown in figure 3:

| press key | :           | display:   | comments:                                 |

|-----------|-------------|------------|-------------------------------------------|

| RST       |             | XX XX XX   | t tot Bankan                              |

| AD        | Ø Ø E 2     | ØØ E2 XX   | initialisation                            |

| DA        | Ø Ø         | ØØ E2 ØØ ( | set the BEGAD pointer                     |

| +         | Ø 2         | ØØ E3 Ø2 ( |                                           |

| +         | FF          | 00 E4 FF   | set the ENDAD pointer                     |

| +         | Ø 3         | ØØ E5 Ø3   |                                           |

| AD        | 1 C B 5     | 1C B5 20   |                                           |

| GO        |             | 77         | start the editor (Cold start entry)       |

| INSERT    | F F 1 Ø Ø Ø | FF 10 00   | enter label number 10 (DISPLAY)           |

| INPUT     | A 9 Ø Ø     | A9 ØØ      | LDA # ØØ                                  |

| INPUT     | 85F9        | 85 F9      | STAZ-INH                                  |

| INPUT     | 8 5 F A     | 85 FA      | STAZ-POINTL                               |

| INPUT     | 8 5 F B     | 85 FB      | STAZ-POINTH                               |

| INPUT     | F F 1 1 Ø Ø | FF 11 ØØ   | label number 11 (DA)                      |

| INPUT     | 206F1D      | 20 6F 1D   | JSR-GETBYT (6F is not a label number!)    |

| INPUT     | 1010        | 10 10      | BPL to label number 10                    |

| INPUT     | 8 5 E       | 85 XX      | error! Instruction is still to be entered |

|           |             |            | into memory                               |

| INPUT     | 85F9        | 85 F9      | STAZ-INH                                  |

| INPUT     | 8 5 D 7     | 85 D7      | STAZ-HEXL                                 |

| INPUT     | 201200      | 20 12 00   | JSR-HEXDEC (label number 12 is HEXDEC)    |

| INPUT     | 4 C 1 1 Ø Ø | 4C 11 00   | JMP-DA (label number 11 is DA)            |

| INPUT     | FF1200      | FF 12 ØØ   | label number 12 (HEXDEC)                  |

| INSERT    |             |            | error! INSERT instead of INPUT            |

| INPUT  | 2 | Ø | 1 | 4 | Ø | Ø | 20         | 14         | ØØ   | JSR-COMNUM (label number 14 is COMNUM)    |

|--------|---|---|---|---|---|---|------------|------------|------|-------------------------------------------|

| INPUT  | 8 | 5 | F | Α |   |   | 85         | FΑ         |      | STAZ-POINTL                               |

| INPUT  | 8 | 4 | D | 7 |   |   | 84         | D7         |      | STYZ-HEXL                                 |

| INPUT  | 2 | Ø | 1 | 4 | Ø | Ø | 20         | 14         | ØØ   | JSR-COMNUM (label number 14 is COMNUM)    |

| INPUT  | Α | 2 | Ø | 4 |   |   | Α2         | <b>Ø</b> 4 |      | LDX # <b>Ø</b> 4                          |

| INPUT  | F | F | 1 | 3 | Ø | Ø | FF         | 13         | ØØ   | label number 13 (HD)                      |

| INPUT  | Ø | Α |   |   | С | Α | ØA         | EE         | EEEE | press command key, otherwise error! ASL-A |

| INPUT  | С | Α |   |   |   |   | CA         |            |      | DEX                                       |

| INPUT  | D | Ø | 1 | 3 |   |   | DØ         | 13         |      | BNE to label number 13                    |

| INPUT  | Ø | 5 | F | Α |   |   | Ø5         | FΑ         |      | ORAZ-POINTL                               |

| INPUT  | 8 | 5 | F | Α |   |   | 85         | FΑ         |      | STAZ-POINTL                               |

|        | 8 | 4 | F | В |   |   | 84         | FB         |      | STYZ-POINTH                               |

| INPUT  | 6 | Ø |   |   |   |   | 6Ø         |            |      | RTS                                       |

| SEARCH | F | F | 1 | 3 |   |   |            | 13         | ØØ   | search for label number 13                |

| SKIP   |   |   |   |   |   |   | ØΑ         |            |      |                                           |

| SKIP   |   |   |   |   |   |   | CA         |            |      |                                           |

| SKIP   |   |   |   |   |   |   | DØ         | 13         |      |                                           |

| SKIP   |   |   |   |   |   |   | Ø5         | FΑ         |      |                                           |

| SKIP   |   |   |   |   |   |   | 85         |            |      |                                           |

| SKIP   |   |   |   |   |   |   | 84         | FΒ         |      |                                           |

| SKIP   |   |   |   |   |   |   | 6 <b>ø</b> |            |      |                                           |

| SKIP   |   |   |   |   |   |   | 77         |            |      | 77 means: depress the INSERT key!!!!      |

|        | F | F | 1 | 4 | Ø | Ø | FF         | 14         | ØØ   | label number 14 (COMNUM)                  |

| INPUT  | 8 | 4 | D | 8 |   |   | 84         | D8         |      | STYZ-HEXH                                 |

|        |   |   |   |   |   |   |            |            |      |                                           |

Note: The instruction LDY # ØØ was inadvertently forgotten. It can be inserted quite easily with the aid of the INSERT command, Thus:

| INSERT | $A \emptyset \emptyset \emptyset$ | AØ ØØ | LDY # 00  |

|--------|-----------------------------------|-------|-----------|

| SKIP   |                                   | 84 D8 | STYZ-HEXH |

The instruction LDY#00 has now been inserted in front of STYZ-HEXH. This involved a fair amount of work for the computer, while the programmer could sit back and watch. Now the INPUT command will enable us to continue, for a new instruction is to be entered after 84 D8. Thus:

| INPUT | 201500      | 2Ø 15 ØØ   | JSR-SUBTRA (label number 15 is SUBTRA) |

|-------|-------------|------------|----------------------------------------|

| INPUT | 1 8         | 18         | CLC                                    |

| INPUT | A 5 D 7     | A5 D7      | LDAZ-HEXL                              |

| INPUT | 69 Ø A      | 69 ØA      | ADC # ØA                               |

| INPUT | 6 Ø         | 6 <b>Ø</b> | RTS                                    |

| INPUT | FF1500      | FF 15 ØØ   | label number 15 (SUBTRA)               |

| INPUT | 3 8         | 38         | SEC                                    |

| INPUT | A 5 D 7     | A5 D7      | LDAZ-HEXL                              |

| INPUT | E 9 Ø A     | E9 ØA      | SBC # ØA                               |

| INPUT | 8 5 D 7     | 85 D7      | STAZ-HEXL                              |

| INPUT | A 5 D 8     | A5 D8      | LDAZ-HEXH                              |

| INPUT | E 9 Ø Ø     | E9 ØØ      | SBC # ØØ                               |

| INPUT | 3 Ø 1 6     | 3Ø 16      | BMI to label number 16                 |

| INPUT | C 8         | C8         | INY                                    |

| INPUT | 4 C 1 5 Ø Ø | 4C 15 ØØ   | JMP-SUBTRA (label number 15 is SUBTRA) |

| INPUT | FF1600      | FF 16 ØØ   | label number 16 (SUB)                  |

| INPUT | 6 Ø         | 6 <b>0</b> | RTS                                    |

The complete program has now been entered into the Junior Computer. It is advisable to check that everything has been entered correctly. This can be done as follows:

SEARCH FF10

SKIP

SKIP

•

٠

SKIP

Only when the entered program corresponds to the flow chart can the assembler be started.

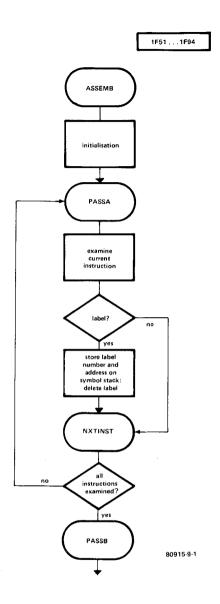

#### The Assembler

We have now entered a program into the computer with the aid of the editor, a program containing symbolic addresses. These consist of label numbers, subroutine numbers or labels to which the computer is to jump or branch. Such a program is not able to run on JC, as in its present form the microprocessor is unable to interpret the instructions. It is up to the assembler to 'shape' the program in such a way that the microprocessor can understand it. The assembler's task consists of:

- \* removing all the labels from the program

- \* assigning the true absolute addresses to the JSR instructions so that they are unambiguous

- \* treating the jump instructions likewise

- \* calculating the correct displacement values for branch instructions

- \* enabling the program to be stored in the programmable memory, after assembly, in an acceptable form for the 6502 microprocessor.

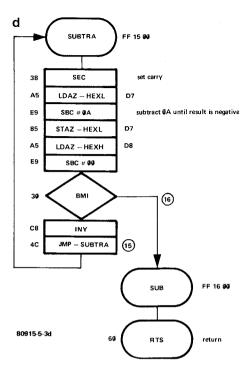

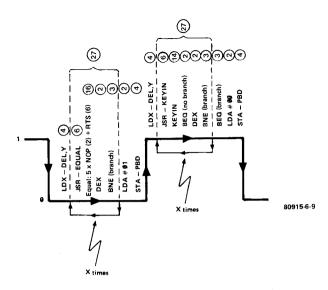

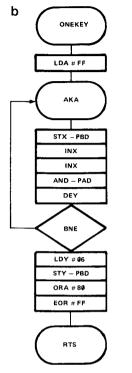

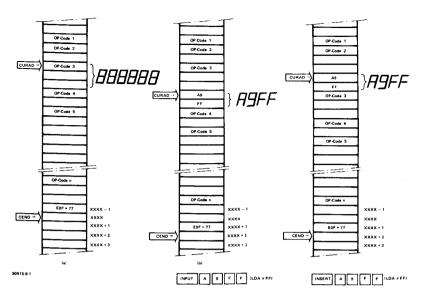

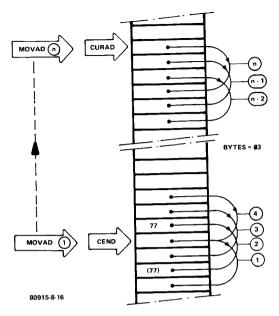

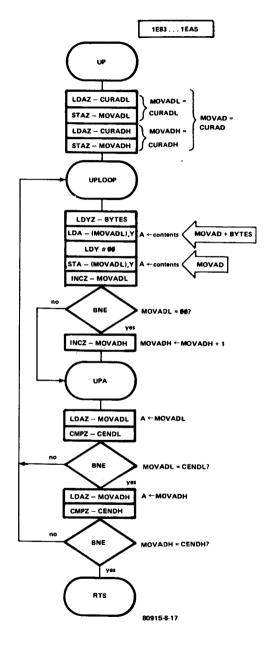

#### How is the program stored in memory before assembly?

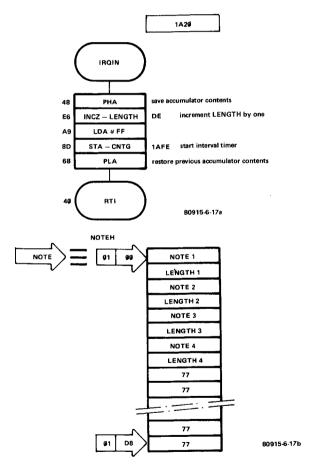

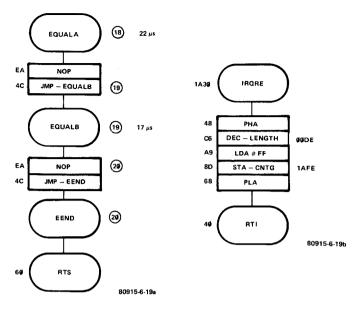

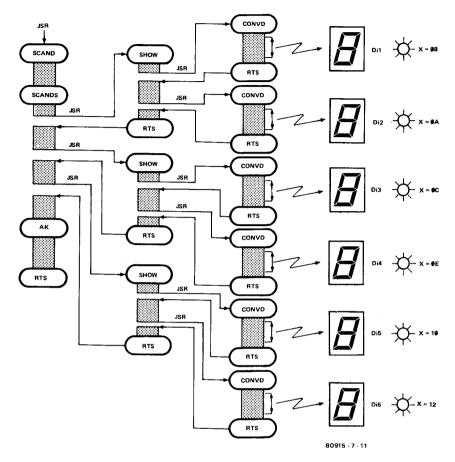

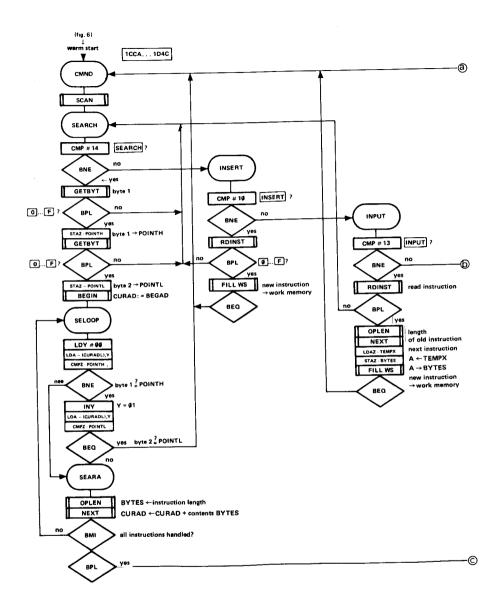

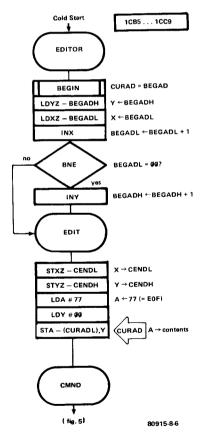

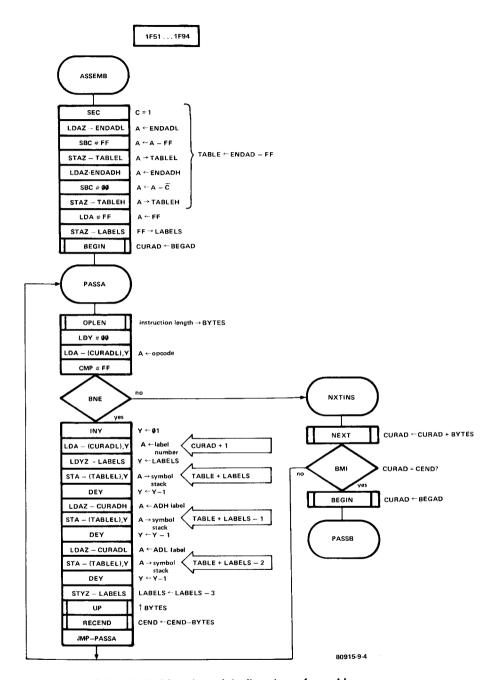

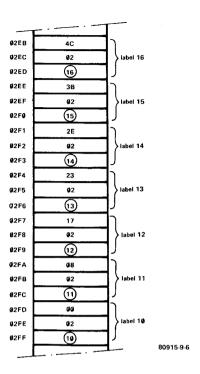

The start address of the program was chosen to be \$200. Figure 4 shows how the editor stored the program in the computer's memory. Since three memory locations were reserved for each label, this program is considerably longer than the assembled version will be. The start address of the assembler is 1F51:

RST call the monitor program

AD 1 F 5 1 enter start address

GO start the assembler

After the GO key is depressed, the display will be blanked for a fraction of a second . . . all that is needed for the computer to assemble the program. If the program was much longer, the display may remain blank for several seconds. As soon as the program has been assembled, the computer will return to the monitor program. The keys AD, DA, +, PC and GO will now be valid once more.

#### How is the program stored in memory after assembly?

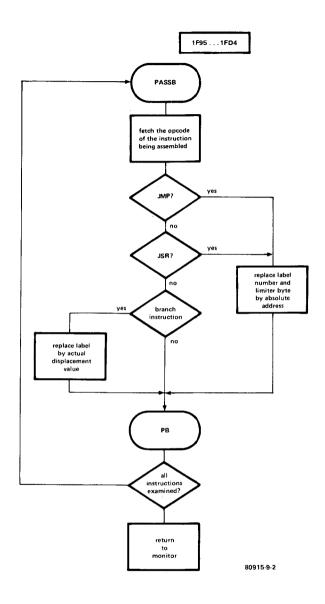

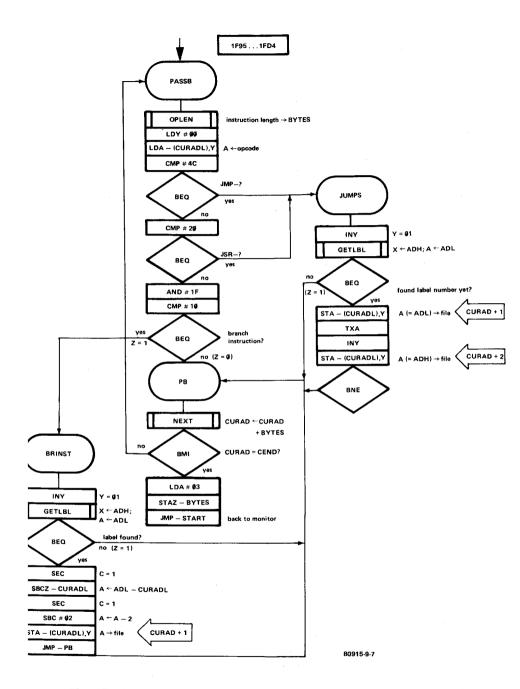

The Junior Computer features a Two Pass Assembler. This means that the program is not assembled in one go, but in two stages, or 'passes'.

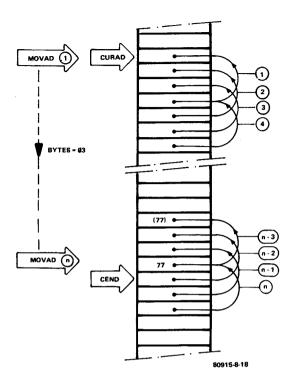

Figure 5. The addressable work space starts at BEGAD and ends at ENDAD. The memory space between the two pointers contains the program starting in this particular example from label FF 10 00 and ending with the EOF character 77. This is called a file. It contains all the instructions that are used in the program, together with their addresses and labels which have the symbolic op-code FF. The Junior Computer cannot 'digest' the program in this form, as both the absolute addresses for jump instructions and the displacements for branch instructions are as yet unknown. The 6502 CPU will not be able to handle the edited data until the program has been assembled.

#### Pass one

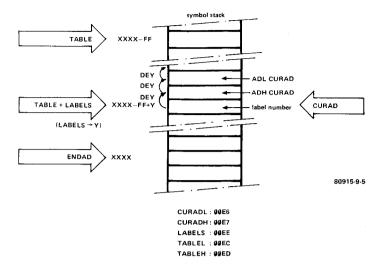

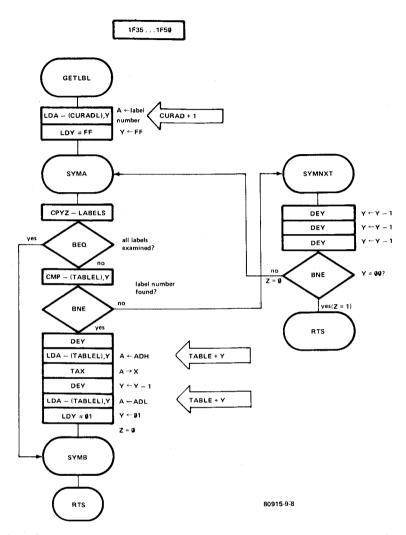

The computer reads the entered program. At this stage it is only interested in the labels written by the programmer and so will ignore all other instructions. If a label is encountered (featuring the characters FF), the label number and its address will be stored in a symbol stack. The latter acts simply as a look-up table and is prepared by the computer without any help from the programmer.

Once the label number and its address have been 'saved' in the symbol stack, the computer will delete the label from the program. This is done by shifting the entire program up by three bytes — the length of the label. The label is overwritten by the instruction(s) immediately following and therefore disappears from the program. The same procedure is repeated until the processor has worked through the whole program from start to finish.

In the example used, the start address was \$200, so the computer will start here. The search continues until another label is found. This will then be added to the symbol stack like its predecessor, along with its address. Eventually, all the labels will have been removed from the program. Everything the computer needs to know about the labels is now being stored inside the symbol stack. This is a 256 byte software register capable of storing up to a maximum of 256/3 = 85 labels. This should be more than enough room to assemble programs in sections.

#### Pass two

Now the assembler will run through the entire program once more, starting at address 0200. As all the labels have already been deleted, the assembler will concentrate on the following instructions only:

- \* JMP-

- \* JSR-

- \* branch instructions such as BPL, BMI, BEQ etc.

These instructions are as yet succeeded by label numbers. When the JC encounters one of the jump instructions, it will look to see which label number follows. Every label number has its own absolute address, which the computer can fetch from the symbol stack. How does it find the correct address in the symbol stack? During the first stage of assembly, remember, the computer saved the label number and its absolute address in the stack. Now the computer will compare the label number behind the jump instruction being assembled with those in the symbol stack. The corresponding absolute address is then inserted after the instruction thereby overwriting the label number and the limiter. The whole procedure is repeated until all the JMP and JSR instructions have been assembled.

This leaves the displacement values for the branch instructions. The next step for the computer, therefore, is to trace all the branch instructions contained in the program. These are still followed by the label numbers to which the branch is supposed to lead. Since the computer knows the address of each branch instruction and since the destination address is stored in the symbol stack, the displacement value can be calculated

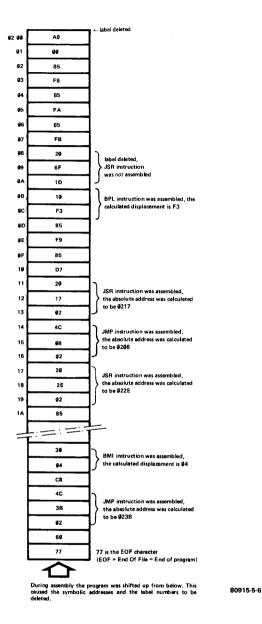

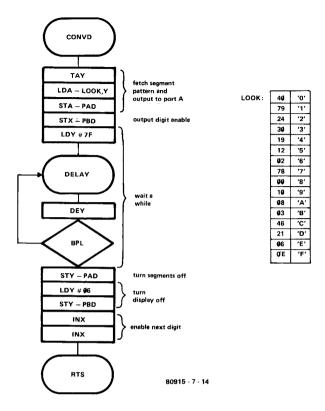

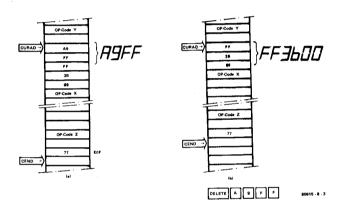

Figure 6. After assembly, all the labels have disappeared from the file, which is why the program looks shorter. The instruction op-codes are now followed by their corresponding absolute addresses. Similarly, displacements have been assigned to the branch instructions. Now the program is acceptable to the 6502 CPU.

without any difficulty:

destination - source + 2 = displacement

which can be translated as: the address location to be branched to, minus the address location where the branch instruction is situated, plus two equals the displacement value. The program given in figure 3 is shown in its assembled form in figure 5.

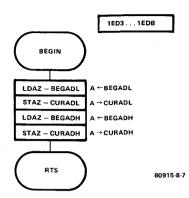

We have now covered the operation of the assembler. It should be added that the editor can also be used to run through an assembled program. The following should then be taken into account:

- \* the editor should only be started by way of a warm start entry (address 1CCA)

- \* the pointers on page zero must be set manually:

BEGAD = CURAD

ENDAD = CEND (CEND = current end address)

Based on the example given in figure 3, the following keys are to be depressed for the editor to be used on an already assembled program.

```

AD Ø Ø E 6

DA Ø Ø }

+ Ø 2 }

set CURAD pointer to 0200

+ FF)

set CEND pointer to Ø3FF

ØЗŚ

+

AD 1 C C A

warm start entry

GO

start the editor

```

This procedure enables the SKIP key to be used to run through an assembled program. The SEARCH command gives the programmer the additional possibility to search for certain instructions inside the assembled program. The INSERT, INPUT and DELETE keys should only be used when entry or deletion of instructions will leave any jump or branch instruction absolute addresses and length - as calculated by the computer - unimpaired.

#### Important addresses for the editor and assembler:

Editor

Cold start entry : \$ 1CB5 Warm start entry: \$1CCA Pointers belonging to the editor:

BEGADL \* \$ 00E2 begin address pointer BEGADH \* \$ 00E3

ENDADL \* \$ 00E4) end address pointer

ENDADH \* \$ 00E5

CURADL \* \$ 00E61 current address pointer

CURADH \* \$ 00E75

\* \$ 00E8 \ current end address pointer CENDL

\* \$ 00 E9 CENDH

2. Assembler:

Start address: \$ 1F51

3. Further possibilities for the editor and assembler:

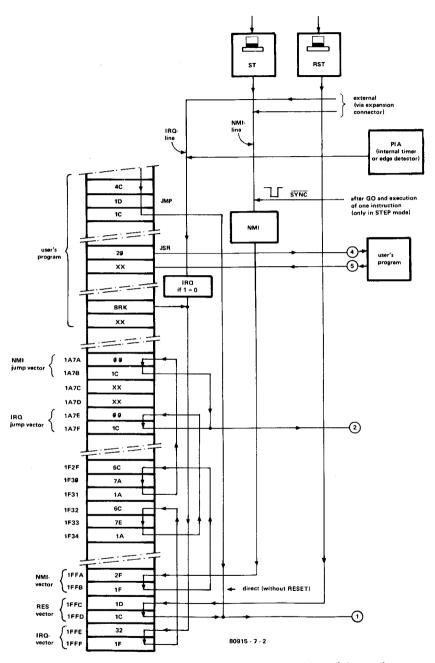

The ST key on the computer's keyboard is linked to the NMI circuit. The NMI-vector can be programmed so that either the editor or the assembler can be started by depressing the ST key. The NMI-vector is stored in address locations:

NMIL \* \$ 1A7A low-order address byte

NMIH \* \$ 1A7B high-order address byte

By loading the start addresses into these locations the programmer can call up either the editor or the assembler with the ST key:

AD 1 A 7 A cold start entry via ST key

DAB5

+ 1 C

or

AD 1 A 7 A warm start entry via ST key

DA C A

+ 1 C

or

AD 1 A 7 A start the assembler via ST key

DA 5 1

+ 1F

We have now reached the point where we are able to operate the editor and assembler contained in the monitor program. These special features make it possible to enter and alter programs quickly and efficiently. This saves the programmer a lot of work — which is what computers are designed for! The editor and the assembler enable programs to be stored in memory in one 'lump', without gaps. This is very important when only a limited amount of memory space is available.

# The Peripheral Interface Adapter or PIA

The Junior Computer possesses a peripheral interface adapter which, like the CPU, is contained in a 40-pin IC. This multifunction device, called PIA for short, takes care of the entire data exchange between the outside world and the Junior Computer. The outside world can assume various forms: it can be a hexadecimal keyboard, a seven-segment display, an ASCII keyboard (simular to that of a typewriter), a printer or even a servo from a model aircraft. This chapter will describe the way in which the computer controls peripheral devices connected to it, how it receives and transmits data via the PIA and how this data is processed.

A computer without any inputs or outputs would be a virtually useless machine, for then it would be unable to communicate with the operator, who plays an essential part in the execution of a program. The situation would be rather like that of a university professor who, having reached a high level in scientific research, is unable to impart any knowledge to his students due to a total lack of vocabulary. Similarly, if a computer did not react to the inaptitude and inconsistency of the (human) programmer, the latter would never learn how to operate the computer correctly.

How can a computer communicate its 'thoughts' to the outside world? The data exchange that takes place between the operator and the computer is just like a conversation between two people. To be able to pass on thoughts and ideas stored in his brain, man uses language. The computer also has thoughts and ideas, stored in the memory in the form of processed data. When such data is to be imparted to the outside world the computer makes use of a printer or, as in the case of the Junior Computer, a six digit (alpha) numeric display.

To be able to follow a conversation it is just as important to listen as it is to talk, for this is the only way to receive information from the person

you are talking to and in fact the only way to find out whether you are "getting through" to him. The computer "listens" by means of a keyboard on which the incoming data is typed. In large(r) computers this will be an ASCII keyboard, but the basic Junior Computer is quite content with a hexadecimal version.

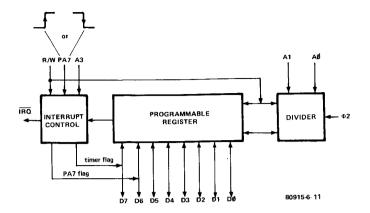

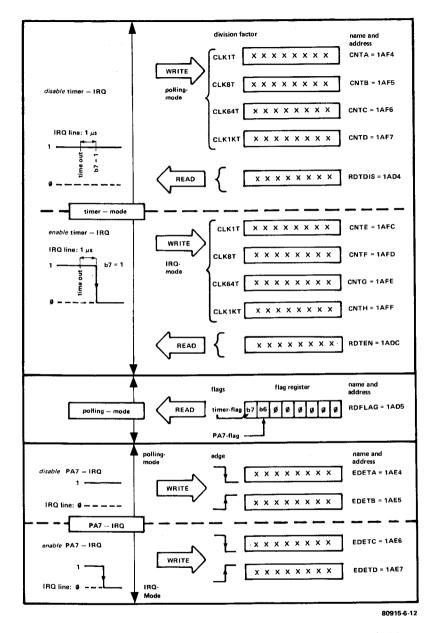

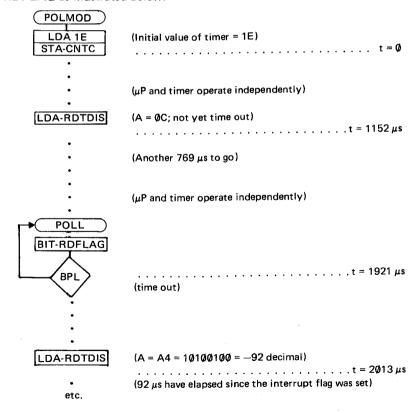

Just as a person uses his mouth to speak and his ears to listen, the Junior Computer transmits and receives information via the PIA. Therefore, the PIA must have suitable inputs and outputs to receive and transmit data, respectively. The term "data" refers to electrical signals which are either logic Ø or logic 1, and which change from one level to the other. The PIA in the Junior Computer is a 6532 type. This LSI (large scala integration) device contains 128 memory locations, a timer which can be programmed in a number of ways, a flag register and an edge detector that can respond to either positive or negative going pulses.

The PIA can be thought of as being a micro-microprocessor which can be programmed to carry out various instructions by means of 19 special 'registers'. Their operation and the numerous ways in which they can be programmed will be fully explained in the course of this chapter.

An overall summary of the 19 registers is given in the following table:

- 1. PORT A and PORT B

- PAD: PORT A Data Register

- PADD: PORT A Data Direction Register

- PBD: PORT B Data Register

- PBDD: PORT B Data Direction Register

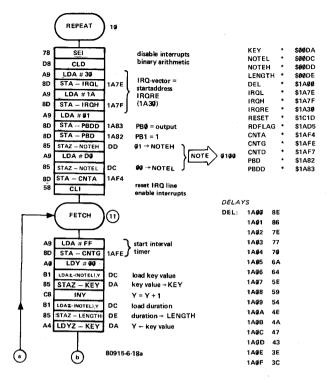

- 2. Timer start; interrupt request is disabled

- CNTA: CLK1T (division factor = 1)

- CNTB: CLK8T (division factor = 8)

- CNTC: CLK64T (division factor = 64)

- CNTD: CLK1KT (division factor = 1024)

- 3. The flag register and timer

- RDFLAG read the flag register

- RDTEN read timer and enable IRQ

- RDTDIS read timer and disable IRQ

- 4. Timer start; interrupt request is enabled

- CNTE: CLK1T (division factor = 1)

- CNTF: CLK8T (division factor = 8)

- CNTG: CLK64T (division factor = 64)

- CNTH: CLK1KT (division factor = 1024)

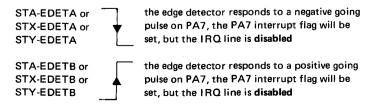

- 5. PA7 as the edge detector

- EDETA: sensitive to negative edge, PA7-IRQ disabled

- EDETB: sensitive to positive edge, PA7-IRQ disabled

- EDETC: sensitive to negative edge, PA7-IRQ enabled

- EDETD: sensitive to positive edge, PA7-IRQ enabled

Each register will be dealt with in turn.

#### PORT A and PORT B

The 6532 contains two ports: PORT A and PORT B. Together they provide the input and output connections for the peripheral interface adapter. Each of the sixteen lines can be individually programmed as an

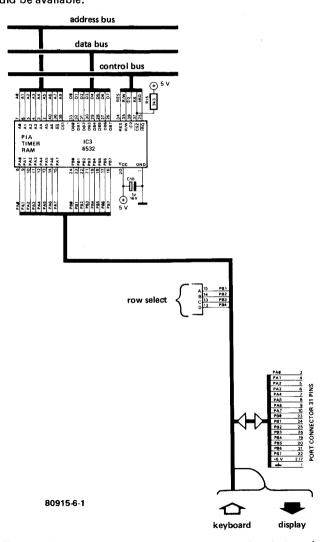

input or an output. The operator can connect various forms of peripheral equipment to any of the input/output lines. In the Junior Computer each of the sixteen lines is fed to a multi-way connector, or port connector. Figure 1 shows that the hexadecimal keyboard and display are also connected to the PIA, so that the operator does not have the full 16 lines at his/her disposal. The lines that can be used are PA7, PBØ and PB5... PB7. If the keyboard and display were made redundant, however, all the port lines would be available.

Figure 1. The hexadecimal keyboard and display are connected to the input/output ports of the PIA. The remaining port lines, PA7, PBØ and PB5 . . . PB7 can be used for the operator's programs.

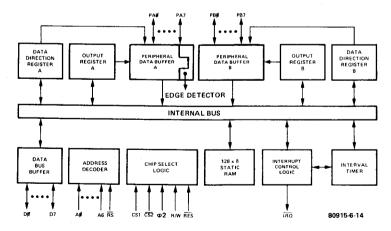

#### The internal structure of the PIA

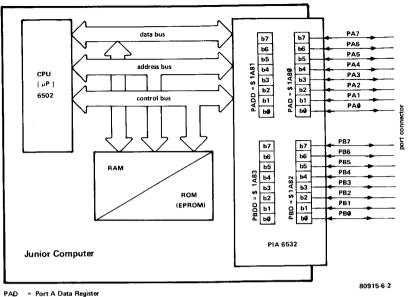

A similar diagram to that shown in figure 1b (Book 1, chapter 3) for the microprocessor may be drawn for the PIA. It is given in figure 2.

The PIA is connected to the microprocessor by means of three buses: the data bus, the address bus and the control bus. Thus, it is connected to the CPU just like any other "normal" memory device. The three buses operate as follows:

- The address bus selects internal memory locations.

- The data bus allows bi-directional data transfer between the CPU and the PIA. The direction of data transfer is controlled by the R/W line connected to the processor.

- The CPU transmits the following signals to the PIA by way of the control bus:

- \* the R/W signal

- \* the  $\Phi 2$  clock signal

- \* the CS2 signal

- \* and the RES (reset) signal

The IRQ line of the PIA is also connected to the CPU by means of the control bus. The PIA can therefore request an interrupt. How this is put into effect will be discussed later.

This covers all the connections between the PIA and the microprocessor. It is now time to take a closer look at the 'internal organs' of the PIA. When discussing the PIA, hardware and software are equally important. The operator sees the PIA as:

- Hardware: sixteen lines which can be independently programmed as inputs or outputs. They are divided into two sections: port A and port B. Both ports consist of eight lines each, that is to say, they are 8 bits wide. The port lines are called PAØ...PA7 and PBØ...PB7. The data bus is connected to the individual port lines and, as there are two ports, it can be switched either to port A or to port B. Since the data bus is bi-directional, the CPU may write onto the port lines, or read data from them. When the microprocessor writes a certain bit pattern onto port lines which have been programmed as outputs, this pattern will remain stored on the output port lines, even after the write operation has ceased (latch function of an output port line).

- When the microprocessor reads one or more port lines which have been programmed as inputs, the logic level present at that instant will be read (there is no latch function for an input port line).

- Software: four registers for storing or retrieving data. They are:

- PAD = PORT A Data register

- PADD = PORT A Data Direction register

- PBD = PORT B Data register

- PBDD = PORT B Data Direction register

As can be seen, each port is made up of two registers:

- 1. a data register

- 2. a data direction register

The data direction register controls the direction of data transfer for each individual port line. As this register is 8 bits wide, the CPU can write a word into the data direction register by means of the data bus.

PADD = Port A Data Direction Register

PBD = Port B Data Register

PBDD = Port B Data Direction Register

Figure 2. The internal view of the peripheral interface adapter (PIA). It contains two ports, each with eight input/output lines. The contents of the data direction registers determine whether a particular port line is to be used as an input or as an output. The PIA is connected to the CPU by means of the address bus, the data bus and the control bus.

This word will be a bit pattern of "noughts" and "ones" and will have the following effect on the port lines:

- a nought in any position in the data direction register will program the corresponding port line to be an input.

- a one in any position in the data direction register will program the corresponding port line to be an output.

In the Junior Computer the four registers have been assigned the following address locations:

PAD : \$ 1A80 PADD : \$ 1A81 PBD : \$ 1A82 PBDD : \$ 1A83

Now for a few examples to familiarise ourselves with port programming. To start with, several port lines are to be programmed either as inputs or outputs.

All the port lines belonging to port A are to be inputs, while all those belonging to port B are to be outputs. The program will then look like this: LDA # 00 all bits in the accumulator are zero STA-PADD lines PA0 . . . PA7 are inputs

LDA # FF all bits in the accumulator are ones

STA-PBDD lines PBØ . . . PB7 are outputs

As you know, the individual bits in the port data direction register determine whether a port line is an input or an output. In the data direction register PADD they are all noughts, so that the port A lines are all programmed as inputs. The CPU can now read the data on the port lines and enter that data into the accumulator, the X register or the Y register. This will be further described later on. In the data direction register PBDD all the bits are ones, causing all the lines to port B to be programmed as outputs. The CPU can now write any bit pattern onto the port lines by way of the data bus. Again, this will be expanded on later.

2. Port lines PA4 and PBØ are to be outputs; the other port lines are to be inputs. The following bit patterns are therefore entered into the two data direction registers:

PADD b7 b6 b5 b4 b3 b2 b1 hØ Ø Ø 1 Ø Ø Ø Ø PBDD b7 b6 b5 b4 b3 b2 b1 bØ Ø Ø Ø Ø 1

The program for the above will be:

LDA # 10 load accumulator with required bit pattern

STA-PADD line PA4 is an output

LDA # Ø1 load accumulator with required bit pattern

STA-PBDD line PBØ is an output

All the other port lines are programmed as inputs.

# Reading from and writing to the port lines

We now know that the port lines can be programmed as inputs or outputs by the information contained in the data direction registers, but how can the microprocessor read or write data from or to them? This facility is provided by the two data registers, PAD and PBD.

Reading port lines PAØ . . . PA7 and PBØ . . . PB7

When the data registers PAD or PBD are read, the bit pattern on the port lines at that moment is transferred, via the data bus, to one of the internal CPU registers. In other words, the port lines are an extension of the data bus. If the processor is to read one or more port lines, they must be programmed as inputs.

The following example illustrates this:

LDA # 00

STA-PADD PAØ...PA7 are programmed as inputs

LDX-PAD the bit pattern on the port lines is stored in the X register of the CPU

If the bit pattern at port A is 10101110,

PA7 PA6 PA5 PA4 PA3 PA2 PA1 PAØ Port A lines

1 Ø 1 Ø 1 1 1 Ø bit pattern

the hexadecimal number AE will be stored in the X register.

If the voltage on a particular port line is less than 0.4 V, the microprocessor will interpret it as logic "0". The voltage must be greater than 2.4 V for a logic "1" to be read.

**Note:** If a port line programmed as an input is connected to the output of a gate, a transistor or another type of logic device, a current of up to 1.6 mA could be produced. This must be taken into account, especially when connecting certain CMOS ICs, so as not to destroy the particular device. When the microprocessor reads the port lines the bit pattern present at that moment will be transferred to one of the CPU registers. Port lines programmed as inputs **do not** therefore, have a latch function.

#### Writing to port lines PAØ . . . PA7 or PBØ . . . PB7

When writing to data registers PAD or PBD, the bit pattern contained in one of the CPU registers will be transferred to the port lines, which can be considered as an extension of the data bus. If the processor is to write to one or more port lines, they must be programmed as outputs. This is illustrated by the following:

LDA # FF

STA-PADD PAØ...PA7 are programmed as outputs

LDX # C3

STX-PAD the bit pattern contained in the X register is transferred to port A lines.

The contents of the X register is C3 = 11000011. This bit pattern will appear on port lines PA7...PA0:

PA7 PA6 PA5 PA4 PA3 PA2 PA1 PAØ port A lines 1 1 Ø Ø Ø Ø 1 1

The hexadecimal number C3 will remain on the port lines until the next write operation (latch function).

Note: If a port line programmed as an output is connected to the input of a gate, a transistor or another type of logic device, these may not draw more than 1.6 mA from the output port. The port lines are only capable of driving one standard TTL load. If TTL compatibility is not required, port lines PBØ...PB7 may be used as a current source to directly drive the base of a transistor switch (maximum of 3 mA at 1.5 V).

Warning! The port lines of the PIA are not protected against excess voltage or current. When they are directly connected to an external device such as a printer, the voltage at the port lines should be prevented from exceeding +7 V or from becoming negative, for then the 6532 is likely to go up in smoke!!

#### First steps

Now that we have discovered all there is to know about port lines, it is high time to write a short demonstration program which uses all four I/O registers. The program should achieve the following:

- 1. At port A the state of eight switches is to be read by the CPU.

- The Junior Computer is to convert this information into an audible signal.

- 3. The signal is to be fed out of PBØ. An amplifier must be provided to control a small 8  $\Omega$  loudspeaker.

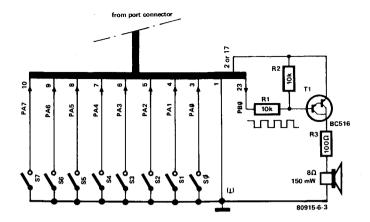

Figure 3. The hardware required for the DEMO program of figure 4. The bit pattern produced by the (closed) switches is read into the computer via port A. This information is then converted into a squarewave signal which is fed to the loudspeaker amplifier via port line PBØ.

- A circuit diagram must be drawn to show how these requirements are to be met.

- 5. Subsequently, a flow chart must be drawn so that the program can be entered into the computer via the editor and then assembled.

Points 1...3 will be fulfilled by the program itself. Point 4 tackles the problem by producing a circuit diagram. This is given in figure 3 and shows how eight switches SØ...S7 are connected to port lines PAØ...PA7. Since the Junior Computer must read the state of these switches (whether they are on or off), all port A lines must be programmed as inputs. An audible signal is to be produced at PBØ, this line must, therefore, be programmed as an output. Transistor T1 is included to enable the signal to be heard via a loudspeaker. This completes the necessary hardware to solve the problem.

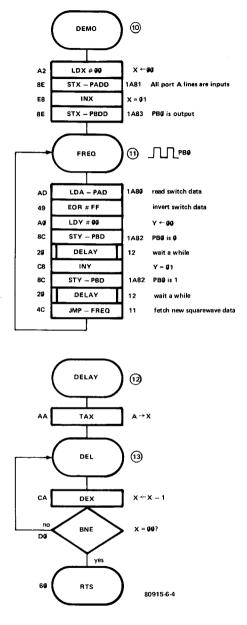

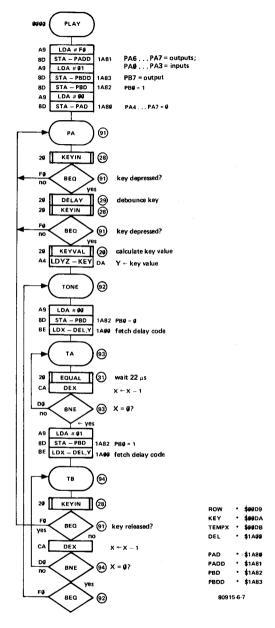

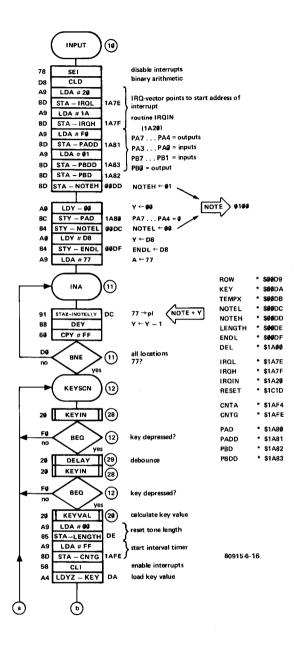

Next, the software, the program (point 5) must be developed. Figure 4 gives a program which converts the switch information into a particular frequency or squarewave. It should be noted that this program is not particularly elegant, but it serves the purpose of illustrating how the four I/O registers PAD, PADD, PBD and PBDD are controlled.

At the start of the demonstration program, DEMO, port lines PAØ...PA7 are programmed as inputs and port line PBØ as an output. All the bits in the data direction register PADD are zero and bØ in the data direction register PBDD is a one. This situation will remain unchanged throughout the program. The following part of our program involves the frequency loop (label FREQ). Here, the processor reads the state of the switches SØ...S7 into the accumulator. Prior to this we must decide whether a closed switch corresponds to a logic one or to a logic nought level:

- a closed switch is logic 1

- an open switch is logic Ø

Figure 4. The flowchart of the DEMO program which, with the hardware from figure 3, will produce a separate tone for each individual key (or combination of keys). The program can be entered into the Junior Computer with the aid of the editor and assembler contained in the monitor program.

After the bit pattern present on the port lines has been copied into the accumulator (LDA-PAD), it must be inverted: EOR # FF. An audible signal must now be produced which is dependent on the switch information. The easiest way to achieve this is to alternately set the output port line PBØ high and low for a certain amount of time. This will effectively produce a squarewave signal which can be rendered audible by means of the loudspeaker interface connected to PBØ.

The Y register is used to "swing" the port line PBØ high and low. The least significant bit (bØ) alternates from nought to one and is copied into the data register PBD. Subroutine DELAY determines the length of time that is high or low. Here the CPU copies the bit pattern of the switch information into the X register (TAX). Then the X register is decremented until it becomes zero. The amount of time this process takes depends on the state of the switches. Thus, the processor is able to generate a whole range of frequencies.

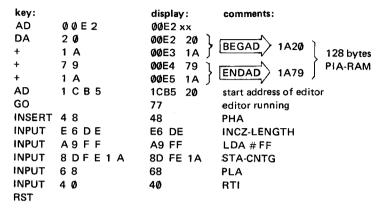

### Editing and assembling the DEMO program

Once the flow chart has been drawn up, the program can be entered into the computer. It is to be assembled in page zero, where locations 0000...00E0 are available. For this reason the BEGAD pointer is set to 0000 and the ENDAD pointer to 00E0. By placing the start address of the assembler 1F51 in locations 1A7A and 1A7B (the NMI vector), the assembler can be started by pressing the ST key. The editor will then be exited from via a non-maskable interrupt. The "keying-in" procedure shown below illustrates how the DEMO program is entered:

| keyboard |   |   |   |   |   |   | display   | comments                     |

|----------|---|---|---|---|---|---|-----------|------------------------------|

| RST      |   |   |   |   |   |   |           |                              |

| AD       | Ø | Ø | Ε | 2 |   |   | ØØE2 XX   |                              |

| DA       | Ø | Ø |   |   |   |   | ØØE2 ØØ l | BEGAD = 0000                 |

| +        | Ø | Ø |   |   |   |   | ØØE3 ØØ ∫ | BEGAD - WWW                  |

| +        | Ε | Ø |   |   |   |   | ØØE4 EØ { | ENDAD = ØØEØ                 |

| +        | Ø | Ø |   |   |   |   | ØØE5 ØØ 🦠 | ENDAD - WEW                  |

| AD       | 1 | Α | 7 | Α |   |   | 1A7A XX   |                              |

| DA       | 5 | 1 |   |   |   |   | 1A7A 51 ) | NMI vector = 1F51            |

| +        | 1 | F |   |   |   |   | 1A7B 1F ∫ | (start address of assembler) |

| AD       | 1 | С | В | 5 |   |   | 1CB5 20   | start address of editor      |

| GO       |   |   |   |   |   |   | 77        | editor running               |

| INSERT   | F | F | 1 | Ø | Ø | Ø | FF 10 00  | label 10: DEMO               |

| INPUT    | Α | 2 | Ø | Ø |   |   | A200      | LDX # ØØ                     |

| INPUT    | 8 | Ε | 8 | 1 | 1 | Α | 8E 81 1A  | STX-PADD                     |

| INPUT    | Ε | 8 |   |   |   |   | E8        | INX                          |

| INPUT    | 8 | Ε | 8 | 3 | 1 | Α | 8E 83 1A  | STX-PBDD                     |

| INPUT    | F | F | 1 | 1 | Ø | Ø | FF 11 ØØ  | label 11: FREQ               |

| INPUT    | Α | D | 8 | Ø | 1 | Α | AD 80/1A  | LDA-PAD                      |

| INPUT    | 4 | 9 | F | F |   |   | 49 FF     | EOR # FF                     |

| INPUT    | Α | Ø | Ø | Ø |   |   | AØØØ      | LDY # 00                     |

| INPUT    | 8 | С | 8 | 2 | 1 | Α | 8C 82 1A  | STY-PBD                      |

| INPUT    | 2 | Ø | 1 | 2 | Ø | Ø | 20/12/00  | JSR-DELAY (label 12)         |

| INPUT | С | 8 |   |   |   |   | C8       | INY                     |

|-------|---|---|---|---|---|---|----------|-------------------------|

| INPUT | 8 | С | 8 | 2 | 1 | Α | 8C 82 1A | STY-PBD                 |

| INPUT | 2 | Ø | 1 | 2 | Ø | Ø | 2Ø 12 ØØ | JSR-DELAY (label 12)    |

| INPUT | 4 | С | 1 | 1 | Ø | Ø | 4C 11 ØØ | JMP-FREQ (label 11)     |

| INPUT | F | F | 1 | 2 | Ø | Ø | FF 12 ØØ | label 12: DELAY         |

| INPUT | Α | Α |   |   |   |   | AA       | TAX                     |

| INPUT | F | F | 1 | 3 | Ø | Ø | FF 13 ØØ | label 13: DEL           |

| INPUT | С | Α |   |   |   |   | CA       | DEX                     |

| INPUT | D | Ø | 1 | 3 |   |   | DØ13     | BNE to label 13         |

| INPUT | 6 | Ø |   |   |   |   | 6Ø       | RTS                     |

| ST    |   |   |   |   |   |   | XXXX XX  | start assembler via NMI |

| AD    | Ø | Ø | Ø | Ø |   |   | 0000 A2  | start address of DEMO   |

| GO    |   |   |   |   |   |   |          | start DEMO              |

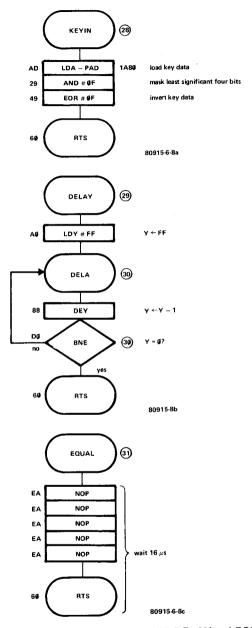

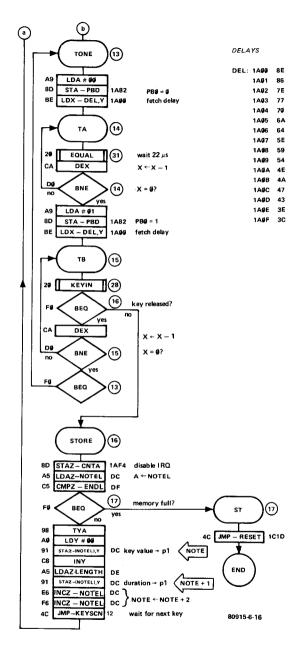

#### Music on the Junior Computer

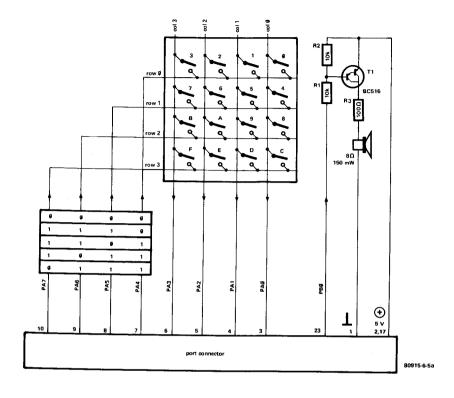

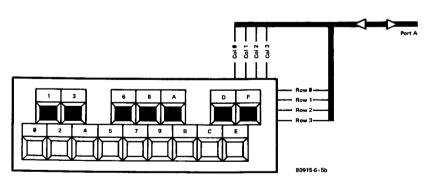

Tunes can be played on the Junior Computer by connecting a small keyboard to port lines. The melody played can be heard via a simple loudspeaker interface. Construction of the Junior "piano" involves the following requirements:

- The keyboard should have black and white keys similar to that of a piano or organ.

- 2. The keys should be arranged in an electrical matrix and the entire keyboard must be connected to port A.

- 3. The tones must be audible!!

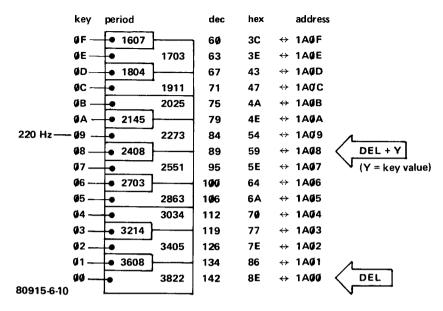

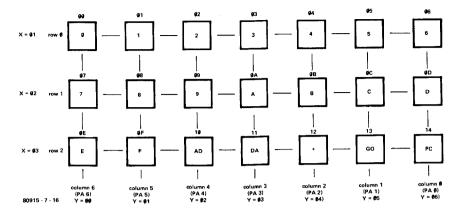

A summary of the requirements is given in figure 5. It includes:

- a piano keyboard

- a key matrix with connections to port A

- an amplifier circuit connected to port line PBØ.

As the keys are arranged in a matrix (figure 5), each key can be assigned a certain value. The matrix format is 4 times 4. The rows are designated as ROW Ø...ROW 3 and the columns as COL Ø...COL 3. The values of the individual keys are also indicated. Figure 5 also shows an alternative construction for the keyboard using Digitast switches.

Since all the keys are connected to only one port (port A), some of the port lines must be used as inputs and some as outputs. Thus:

- Columns COL Ø... COL 3 are connected to PAØ... PA3. Since the computer has to read the column information to calculate key values, port lines PAØ... PA3 will have to be inputs.

- Rows ROW Ø... ROW 3 are connected to PA4...PA7 and must become logic Ø one after the other, so that the computer can detect whether a key is depressed, identify it and calculate its value. As the computer has to write certain patterns onto matrix rows ROW Ø... ROW 3, port lines PA4...PA7 must be outputs.

We have already seen how to connect a simple loudspeaker interface. Again, PBØ ist to be programmed as the sound output.

This covers the mechanical and electrical structure of the "piano" keyboard. Let us now develop a short program that will enable a tune to be played on the keyboard. It must be constructed step by step and should comprise the following:

Figure 5. The hardware required for the PLAY program (see figure 7). The keys are arranged in a four-by-four matrix (5a). Each key will produce a separate note. The frequency codes for each of these notes are contained in the look-up table DEL (see figure 10). Figure 5b shows a possible layout for an inexpensive alternative to a (proper) piano keyboard.

- a routine to calculate the values of the 16 keys

- a routine to establish whether any key is depressed

- a routine to "debounce" the keys

- a routine to allocate a particular frequency to each key that is depressed

- a look-up table in which the 16 key frequencies are stored

Figure 6 shows the flowchart of a program to calculate the value of the 16 keys. Since it scans the key matrix given in figure 5 the I/O lines of port A must be programmed before the processor jumps to this subroutine (KEYVAL). As we know, port lines PA7...PA4 are outputs and PA3..

..PAØ are inputs. Thus, the data direction register belonging to port A must be loaded with the bit pattern 11110000 = FØ. This can be accomplished by the instructions:

LDA # FØ

STA-PADD

All the I/O lines for port A have now been programmed and the subroutine KEYVAL can be called. During its description the key matrix in figure 5 and the flowchart in figure 6 will be referred to.

At the start of the routine memory location ROW is loaded with the value F7 (= 11110111). The X register operates as a row counter, its contents determine which row of the keyboard matrix is being read into the computer via port A:

$X = \emptyset 3$  corresponds to ROW  $\emptyset$

X = Ø2 corresponds to ROW 1

$X = \emptyset 1$  corresponds to ROW 2

$X = \emptyset \emptyset$  corresponds to ROW 3

Each time the X register is decremented, the processor moves the contents of memory location ROW one bit position to the left and stores it in the data register PAD. As a result, the matrix lines will each go low in succession:

| X register               | PA7 PA | 4 |

|--------------------------|--------|---|

| $X = \emptyset 4$        | 1111   |   |

| $X = \emptyset 3$        | 111Ø   |   |

| $X = \emptyset 2$        | 11Ø1   |   |

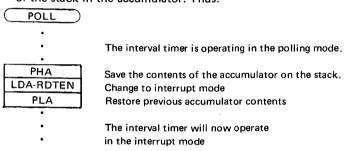

| $X = \emptyset 1$        | 1Ø11   |   |